WM2616 データシートの表示(PDF) - Wolfson Microelectronics plc

部品番号

コンポーネント説明

メーカー

WM2616 Datasheet PDF : 9 Pages

| |||

WM2616

Production Data Rev 1.0

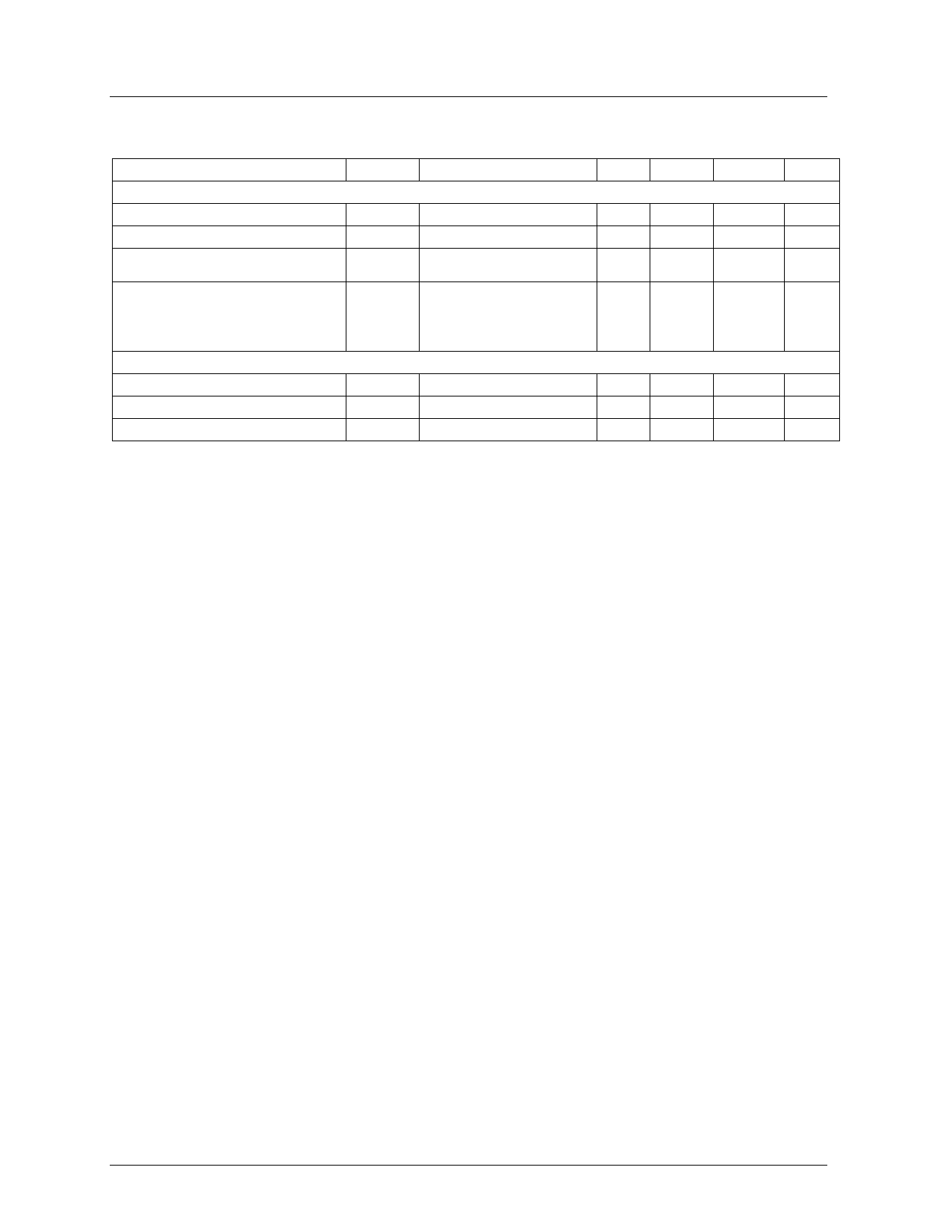

Test Conditions:

RL = 10kΩ, CL = 100pF. VDD = 5V ± 10%, VREF = 2.048V and VDD = 3V ± 10%, VREF = 1.024V over recommended operating free-air

temperature range (unless noted otherwise).

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Reference

Reference input resistance

RREFIN

10

MΩ

Reference input capacitance

CREFIN

5

pF

Reference feedthrough

Reference input bandwidth

Digital Inputs

VREF = 1VPP at 1kHz

-75

+ 1.024V dc, DAC code 0

VREF = 0.2VPP + 1.024V dc

DAC code 2048

Slow

0.5

Fast

1.3

dB

MHz

MHz

High level input current

IIH

Input voltage = VDD

1

µA

Low level input current

IIL

Input voltage = 0V

-1

µA

Input capacitance

CI

3

pF

Notes:

1. Integral non-linearity (INL) is the maximum deviation of the output from the line between zero and full scale (excluding the effects of zero

code and full scale errors).

2. Differential non-linearity (DNL) is the difference between the measured and ideal 1LSB amplitude change of any adjacent two codes. A

guarantee of monotonicity means the output voltage changes in the same direction (or remains constant) as a change in digital input code.

3. Zero code error is the voltage output when the DAC input code is zero.

4. Gain error is the deviation from the ideal full scale output excluding the effects of zero code error.

5. Power supply rejection ratio is measured by varying VDD from 4.5V to 5.5V and measuring the proportion of this signal imposed on the

zero code error and the gain error.

6. Zero code error and Gain error temperature coefficients are normalised to full scale voltage.

7. Output load regulation is the difference between the output voltage at full scale with a 10kΩ load and 2kΩ load. It is expressed as a

percentage of the full scale output voltage with a 10kΩ load.

8. IDD is measured while continuously writing code 2048 to the DAC. For VIH < VDD - 0.7V and VIL > 0.7V supply current will increase.

9. Typical supply current in power down mode is 10nA. Production test limits are wider for speed of test.

10. Slew rate results are for the lower value of the rising and falling edge slew rates

11. Settling time is the time taken for the signal to settle to within 0.5LSB of the final measured value for both rising and falling edges. Limits

are ensured by design and characterisation, but are not production tested.

12. SNR, SNRD, THD and SPFDR are measured on a synthesised sinewave at frequency fOUT generated with a sampling frequency fs.

WOLFSON MICROELECTRONICS LTD

Production Data Rev 1.0 June 1999

4