BF998WR,115 データシートの表示(PDF) - NXP Semiconductors.

部品番号

コンポーネント説明

メーカー

BF998WR,115 Datasheet PDF : 13 Pages

| |||

NXP Semiconductors

N-channel dual-gate MOS-FET

Product specification

BF998WR

30

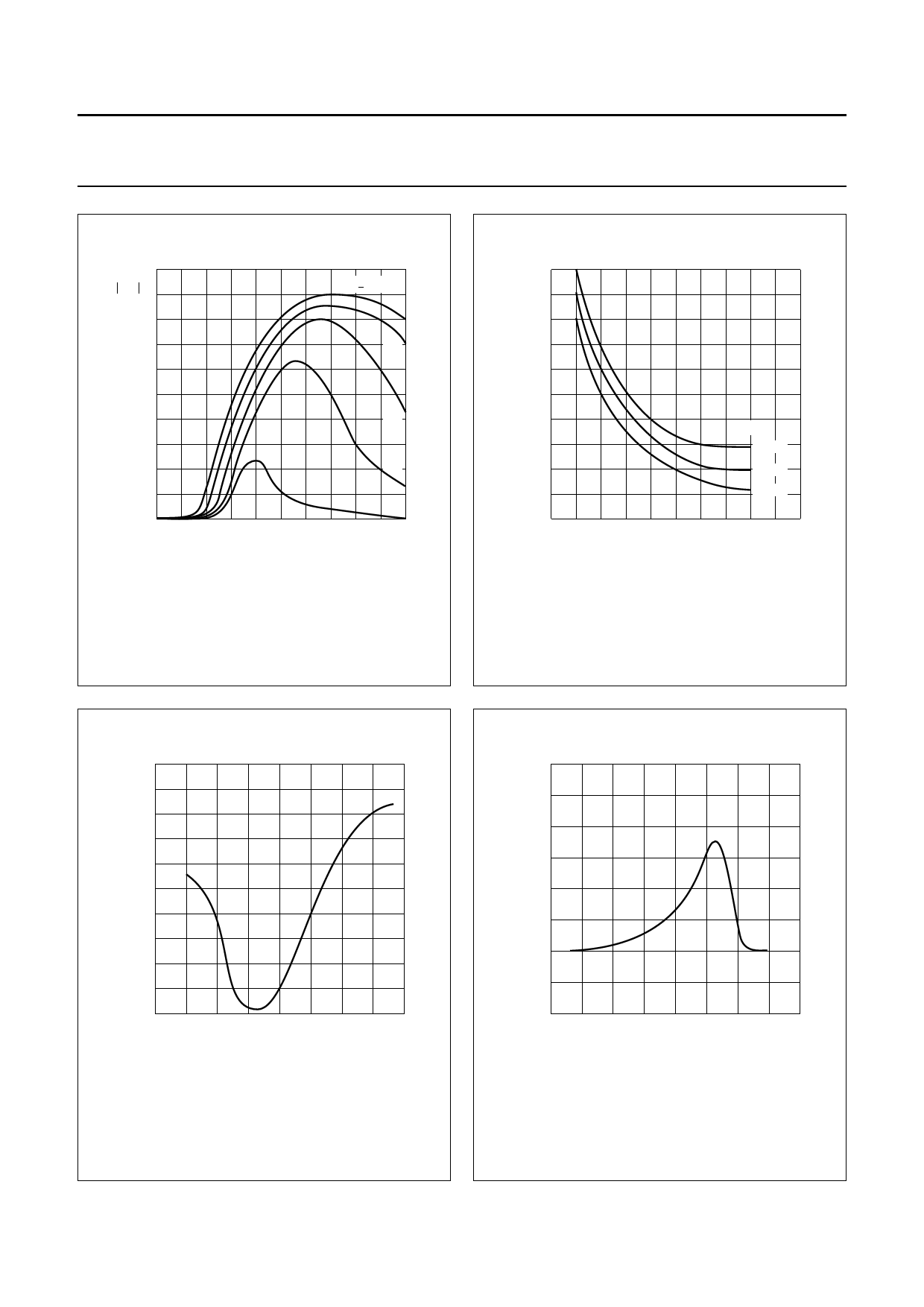

y fs

(mS)

24

18

12

6

0

−1

MGC474

VG2 S = 4 V

3V

2V

1V

0V

0

1

VG1-S (V)

VDS = 8 V; Tamb = 25 C.

Fig.7 Forward transfer admittance as a function

of gate 1 voltage; typical values.

1.5

Cos

(pF)

1.4

MGC475

1.3

1.2

1.1

1.0

4

6

ID =

12 mA

10 mA

8 mA

8

10

12

14

VDS(V)

VG2-S = 4 V; f = 1 MHz; Tamb = 25 C.

Fig.8 Output capacitance as a function of

drain-source voltage; typical values.

2.4

Cis

(pF)

2.2

2.0

1.8

1.6

1.4

−2.4

−1.6

−0.8

MGC476

0

0.8

VG1-S (mV)

2.4

Cis

(pF)

2.3

MGC477

2.2

2.1

2.0

6

4

2

0

−2

VG2-S (V)

VDS = 8 V; VG2-S = 4 V; f = 1 MHz; Tamb = 25 C.

Fig.9 Gate 1 input capacitance as a function of

gate 1-source voltage; typical values.

VDS = 8 V; VG1-S = 0 V; f = 1 MHz; Tamb = 25 C.

Fig.10 Gate 1 input capacitance as a function of

gate 2-source voltage; typical values.

1997 Sep 05

6