CS61304A データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61304A Datasheet PDF : 32 Pages

| |||

CS61304A

CS61304A

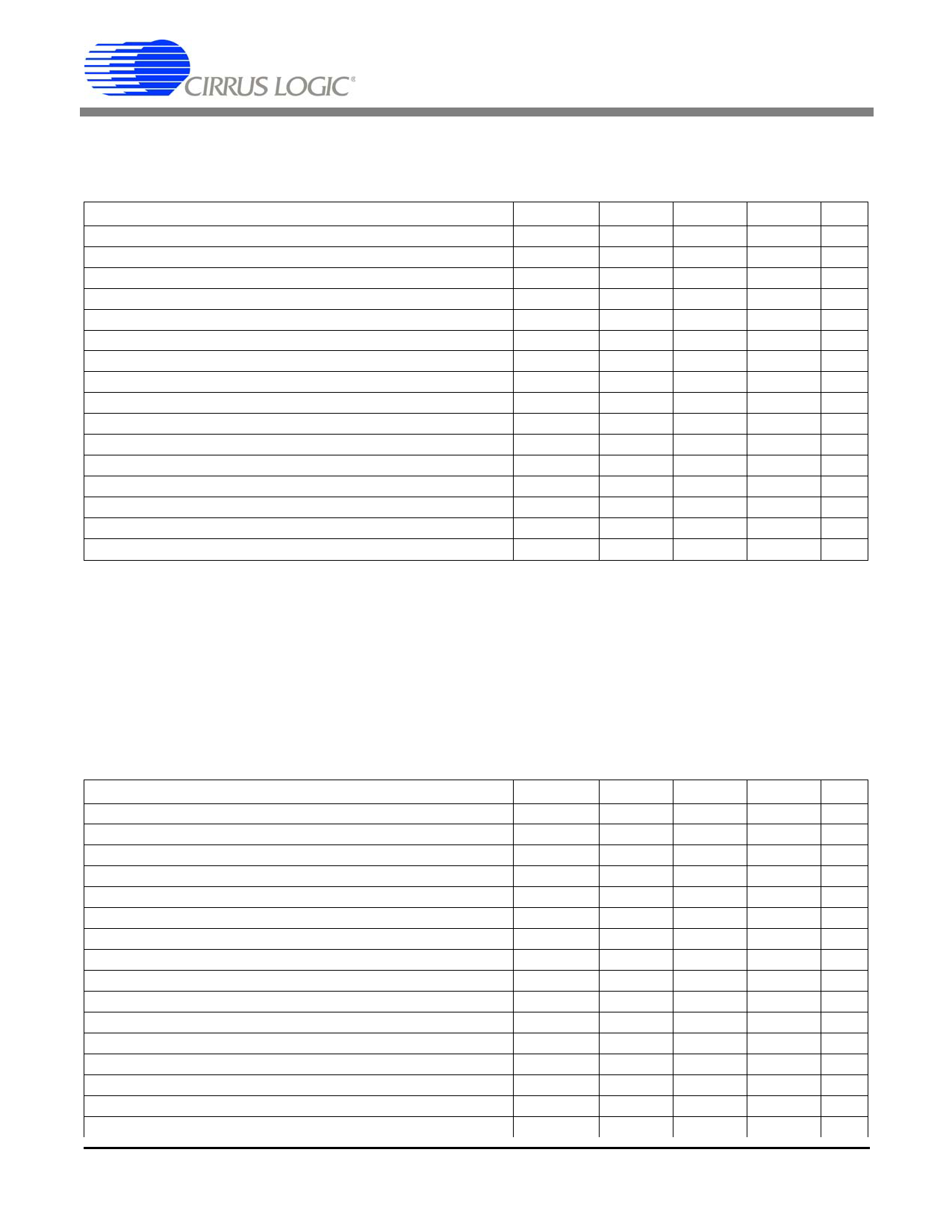

T1 SWITCHING CHARACTERISTICS (TA = -40°C to 85°C; TV+, RV+ = 5.0V ±5%;

GND = 0V; Inputs: Logic 0 = 0V, Logic 1 = RV+; See Figures 1, 2, & 3)

Parameter

Symbol Min

Typ

Max

Crystal Frequency

(Note 25)

fc

- 6.176000 -

TCLK Frequency

ftclk

-

1.544

-

TCLK Pulse Width

(Note 26) tpwh2

150

-

500

ACLKI Duty Cycle

tpwh3/tpw3

40

-

60

ACLKI Frequency

(Note 27) faclki

-

1.544

-

RCLK Duty Cycle

(Note 28) tpwh1/tpw1

45

50

55

Rise Time, All Digital Outputs

(Note 29)

tr

-

-

85

Fall Time, All Digital Outputs

(Note 29)

tf

-

-

85

TPOS/TNEG (TDATA) to TCLK Falling Setup Time

tsu2

25

-

-

TCLK Falling to TPOS/TNEG (TDATA) Hold Time

th2

25

-

-

RPOS/RNEG Valid Before RCLK Falling

(Note 30) tsu1

150

274

-

RDATA Valid Before RCLK Falling

(Note 31) tsu1

150

274

-

RPOS/RNEG Valid Before RCLK Rising

(Note 32) tsu1

150

274

-

RPOS/RNEG Valid After RCLK Falling

(Note 30)

th1

150

274

-

RDATA Valid After RCLK Falling

(Note 31)

th1

150

274

-

RPOS/RNEG Valid After RCLK Rising

(Note 32)

th1

150

274

-

Notes: 25. Crystal must meet specifications described in CXT6176/CXT8192 data sheet.

26. The transmitted pulse width does not depend on the TCLK duty cycle.

27. ACLKI provided by an external source or TCLK.

28. RCLK duty cycle will be 62.5% or 37.5% when jitter attenuator limits are reached.

29. At max load of 1.6 mA and 50 pF.

30. Host Mode (CLKE = 1).

31. Extended Hardware Mode.

32. Hardware Mode, or Host Mode (CLKE = 0).

E1 SWITCHING CHARACTERISTICS (TA = -40°C to 85°C; TV+, RV+ = 5.0V ±5%;

GND = 0V; Inputs: Logic 0 = 0V, Logic 1 = RV+; See Figures 1, 2, & 3)

Parameter

Crystal Frequency

(Note 25)

TCLK Frequency

TCLK Pulse Width

(Note 26)

ACLKI Duty Cycle

ACLKI Frequency

(Note 27)

RCLK Duty Cycle

(Note 28)

Rise Time, All Digital Outputs

(Note 29)

Fall Time, All Digital Outputs

(Note 29)

TPOS/TNEG (TDATA) to TCLK Falling Setup Time

TCLK Falling to TPOS/TNEG (TDATA) Hold Time

RPOS/RNEG Valid Before RCLK Falling

(Note 30)

RDATA Valid Before RCLK Falling

(Note 31)

RPOS/RNEG Valid Before RCLK Rising

(Note 32)

RPOS/RNEG Valid After RCLK Falling

(Note 30)

RDATA Valid After RCLK Falling

(Note 31)

RPOS/RNEG Valid After RCLK Rising

(Note 32)

Symbol

fc

ftclk

tpwh2

tpwh3/tpw3

faclki

tpwh1/tpw1

tr

tf

tsu2

th2

tsu1

tsu1

tsu1

th1

th1

th1

Min

Typ

Max

- 8.192000 -

-

2.048

-

150

-

340

40

-

60

-

2.048

-

45

50

55

-

-

85

-

-

85

25

-

-

25

-

-

100

194

-

100

194

-

100

194

-

100

194

-

100

194

-

100

194

-

DS156PFP1 2

Units

MHz

MHz

ns

%

MHz

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Units

MHz

MHz

ns

%

MHz

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

55