ICPL2531 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

メーカー

ICPL2531 Datasheet PDF : 4 Pages

| |||

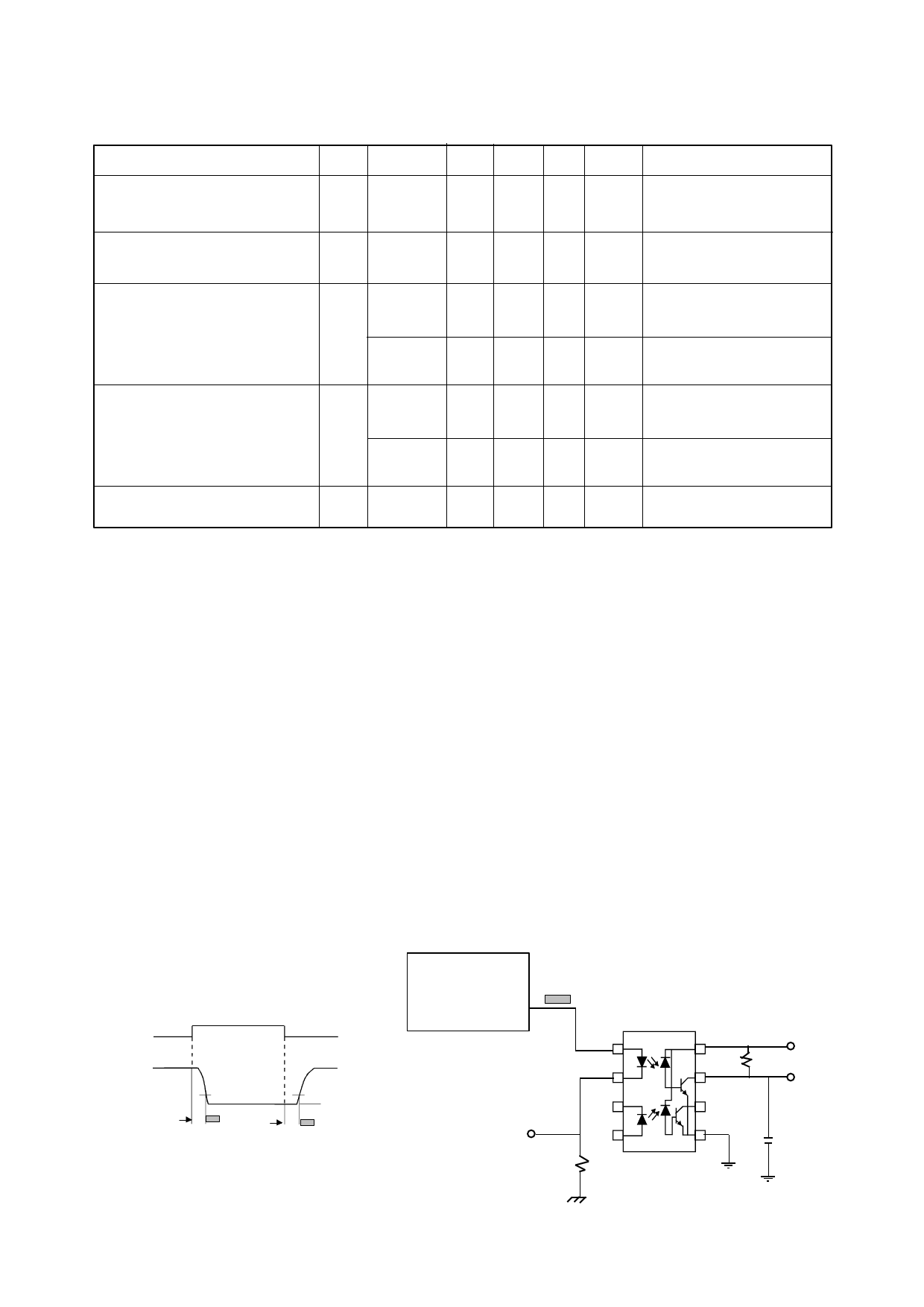

SWITCHING SPECIFICATIONS AT TA = 25°C ( VCC = 5V, IF = 16mA Unless otherwise noted )

PARAMETER

SYM DEVICE MIN TYP MAX UNITS TEST CONDITION

Propagation Delay Time

tPHL ICPL2530

to Logic Low at Output ( fig 1 )

ICPL2531

Propagation Delay Time

t

ICPL2530

PLH

to Logic High at Output ( fig 1 )

ICPL2531

Common Mode Transient

Immunity at Logic High

Level Output ( fig 2 )

ICPL2530

CM

H

ICPL2531

Common Mode Transient

Immunity at Logic Low

Level Output ( fig 2 )

ICPL2530

CM

L

ICPL2531

Bandwidth

BW

0.5 1.5 µs

0.2 0.8 µs

0.5 1.5 µs

0.2 0.8 µs

1000

V/µs

1000

V/µs

-1000

V/µs

-1000

V/µs

3

MHz

RL= 4.1kΩ,(note11 )

RL= 1.9kΩ,(note10 )

R=

L

4.1kΩ,(note11

)

RL= 1.9kΩ,(note10 )

IF = 0mA, VCM = 10VPP

R=

L

4.1kΩ,(note9,11

)

I = 0mA, V = 10V

F

CM

PP

RL = 1.9kΩ,(note9,10 )

VCM = 10VPP

R

L

=

4.1kΩ,(note9,11

)

VCM = 10VPP

RL = 1.9kΩ,(note9,10 )

R

L

=

100Ω,

(note

12

)

NOTES:-

1. Derate linearly above 70oC free air temperature at a rate of 0.8 mA/°C.

2. Derate linearly above 70oC free air temperature at a rate of 1.6 mA/°C.

3. Derate linearly above 70oC free air temperature at a rate of 0.9 mW/°C.

4. Derate linearly above 70oC free air temperature at a rate of 1.0 mW/°C.

5. Each channel .

6. CURRENT TRANSFER RATIO is defined as the ratio of output collector current,I , to the forward LED

O

input current, IF times 100%.

7. Device considered a two-terminal device: pins 1,2,3, and 4 shorted together and pins 5,6,7 and 8 shorted

together.

8. Measured between pins 1 and 2 shorted together, and pins 3 and 4 shorted together.

9. Common mode transient immunity in Logic High level is the maximum tolerable (positive) dVcm/dt on

the leading edge of the common mode pulse V to assure that the output will remain in a Logic High

CM

state (i.e. VO > 2.0V). Common mode transient immunity in Logic Low level is the maximum tolerable

(negative) dVcm/dt on the trailing edge of the common mode pulse signal, VCM to assure that the output

will remain in Logic Low state (i.e. VO< 0.8V).

10. The 1.9kΩ load represents 1 TTL unit load of 1.6mA and the 5.6kΩ pull-up resistor.

11. The 4.1kΩ load represents 1 LSTTL unit load of 0.36mA and the 6.1kΩ pull-up resistor.

12. The frequency at which the a.c. output voltage is 3dB below the low frequency asymptote.

FIG.1 SWITCHING TEST CIRCUIT

IF

0

V

O

t

PHL

1.5V

tPLH

5V

1.5V

V

OL

PULSE

GENERATOR I

F

ZO = 50Ω

tr = 5ns

10% Duty Cycle

1

1/f < 100µs

2

3

I Monitor

4

F

100Ω

8

5V

7

R

L

VO

6

5

C = 15pF

L

7/12/00

DB92030-AAS/A3