HDMP-1646 データシートの表示(PDF) - HP => Agilent Technologies

部品番号

コンポーネント説明

メーカー

HDMP-1646 Datasheet PDF : 15 Pages

| |||

HDMP-1636/46 (Receiver Section)

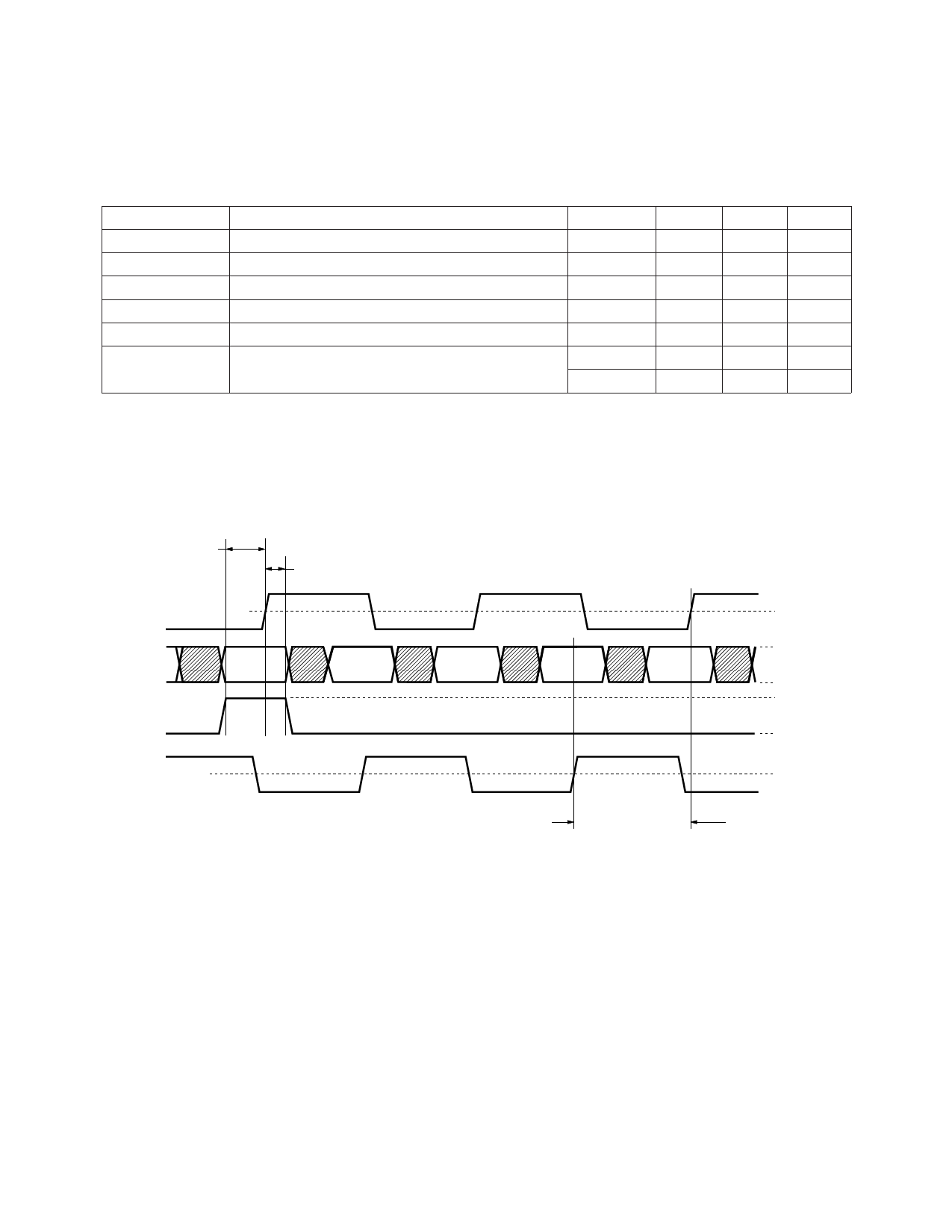

Timing Characteristics

TA = 0°C to +70°C, VCC = 3.15 V to 3.45 V

Symbol

Parameter

b_sync[1,2]

Bit Sync Time

tvalid_before

tvalid_after

Time Data Valid Before Rising Edge of RBC

Time Data Valid After Rising Edge of RBC

tduty

tA-B

t_rxlat[3]

RBC Duty Cycle

Rising Edge Time Difference

Receiver Latency

Units

bits

nsec

nsec

%

nsec

nsec

bits

Min.

2.5

1.5

40

7.5

Typ.

TBD

TBD

7.9

22.4

28

Max.

2500

60

8.5

Notes:

1. This is the recovery time for input phase jumps, per the Fibre Channel Specification X3.230-1994 FC-PH Standard, Sec 5.3.

2. Tested using CPLL = 0.1 µF.

3. The receiver latency, as shown in Figure 6, is defined as the time between receiving the first serial bit of a parallel data word

(defined as the first edge of the first serial) and the clocking out of that parallel word (defined by the rising edge of the receive byte

clock, either RBC1 or RBC0).

,,,,,,,,, tvalid_before

RBC1

tvalid_after

RX[0]-RX[9]

BYTSYNC

K28.5

DATA

DATA

DATA

DATA

1.4 V

2.0 V

0.8 V

2.0 V

0.8 V

RBC0

1.4 V

tA-B

Figure 5. Receiver Section Timing.

Figure 6. Receiver Latency.

716