ADP3020 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

ADP3020 Datasheet PDF : 22 Pages

| |||

ADP3020

THEORY OF OPERATION

The ADP3020 is a dual-mode, step-down power supply controller

for notebook computers or similar battery-powered applications.

The device contains two synchronous step-down buck control-

lers and a linear regulator controller. The buck controllers in the

ADP3020 have the ability to provide either fixed 3.3 V and 5 V

outputs or independently adjustable (1.25 V to VIN–0.5 V) out-

puts. High efficiency over a broad load range is achieved by using a

proprietary dual-mode PWM/power-saving (PSV) mode architec-

ture. Efficiency is further improved by deleting the external current

sense resistor, which is the main contributor to loss during high

current, low output voltage conditions.

CIRCUIT DESCRIPTION

Dual-Mode Architecture

The ADP3020 contains two independent dual-mode, synchro-

nous buck controllers. Traditional constant frequency PWM

buck converters suffer from relatively low efficiency under light

load conditions. In order to maintain high efficiency over a wide

load range, the ADP3020 uses a proprietary dual-mode archi-

tecture. At moderate to heavy loads, the buck converter operates

in the traditional Pulsewidth Modulation (PWM) mode. At light

loads, PSV mode is used to increase system efficiency. A propri-

etary detection scheme is used for transition from one mode to the

other. Input current to the high-side MOSFET is detected when

going from PWM mode to PSV mode, and output voltage infor-

mation is used when changing from PSV mode to PWM mode.

When the high-side N-channel MOSFET is turned on, the current

going through the N-channel MOSFET is measured as a voltage

between CS and SW. If the peak current through the MOSFET

is less than 20% of the current limit value set by CLSET, an

internal counter that is based on the oscillator frequency will be

started. If the current stays below this threshold for 16 PWM

cycles, the buck converter will enter power-saving mode. The

counter will automatically reset if the peak current is higher than

20% of the current limit value any time prior to when the counter

reaches 16.

In PSV mode, the buck converter works like a window regula-

tor. If the output voltage drops below the PWM mode nominal

output voltage, the high-side MOSFET will be turned on. It will

remain on until the output capacitors are charged up to 2%

above the PWM mode nominal output voltage. The high-side

MOSFET will then be latched off until the output capacitors are

discharged to the lower threshold. The discharge rate is depen-

dent on the output capacitor value and load current.

It is important to note that the current limit threshold when in

PSV mode is approximately 1/4 of the current limit threshold

when in PWM mode. If a large load is applied to the converter

when in PSV mode (for example, larger than the current limit in

PSV mode), the output will continue to drop due to the lower

current limit threshold of PSV mode. When the output voltage

drops to 2% below the PWM mode nominal voltage, the converter

will automatically return to PWM mode. Once in PWM mode,

the current limit is quadrupled, and the output will be charged

up to the nominal level, as long as the load does not exceed the

higher PWM current limit.

PWM/PSV Operation (MODE)

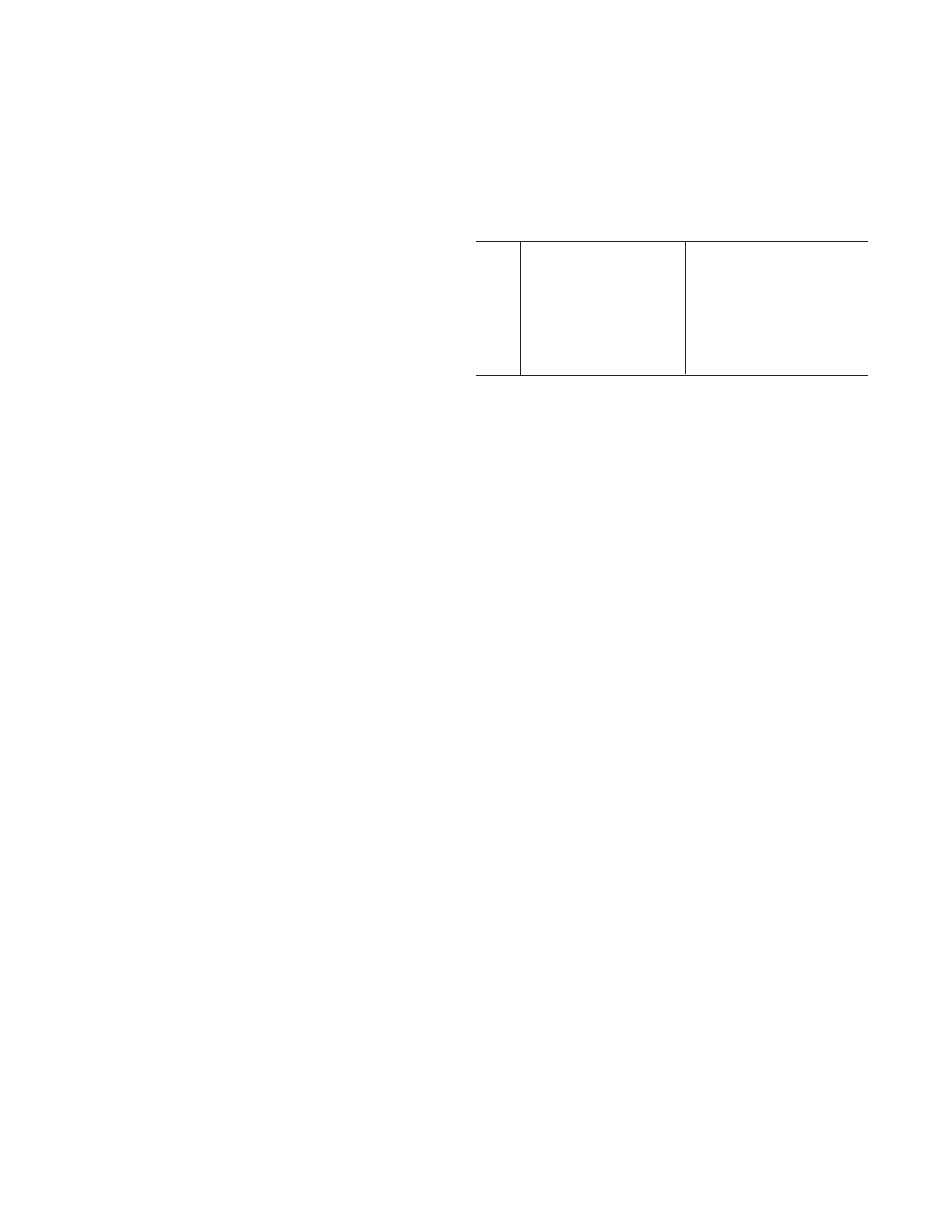

Table I shows the summary of the operating modes of the synchro-

nous buck controllers. The MODE pin determines whether or not

the controllers remain in PWM mode under all load conditions.

MODE can be driven by an external TTL logic signal. When

MODE is pulled HIGH, PSV mode operation is disabled, and

the system is always in constant frequency PWM mode. In order

to enable PSV mode at light loads, the MODE pin needs to be

pulled LOW.

Table I. PWM Mode and PSV Mode

Mode

High

Low

Low

Low

Load

Current

X

Heavy

Moderate

Light

Operating

Mode

PWM

PWM

PWM

PSV

Description

Constant-Frequency PWM

Constant-Frequency PWM

Constant-Frequency PWM

Variable-Frequency, Burst

Mode

X = Don’t Care.

Forcing the ADP3020 to always remain in constant frequency

PWM mode can be used to reduce interference, as this allows

filtering of the fixed fundamental frequency and its harmonics.

The operating frequency should be carefully chosen so that both

the fundamental and harmonic frequencies are not within sensitive

audio or IF bands. This is particularly important in noise-sensitive

applications such as multimedia systems, cellular phones, com-

puters with built-in RF communications, and PDAs. If two or

more switching regulators are used in a system, it is best to syn-

chronize all the switching regulators to a single master regulator

or an external clock signal.

Internal 5 V Supply (INTVCC)

An internal low dropout regulator (LDO) generates a 5 V supply

(INTVCC) that powers all of the functional blocks within the

IC. The total current rating of this LDO is 50 mA. However,

this current is used for supplying gate-drive power, and it is not

recommended that current be drawn from this pin for other

purposes. Bypass INTVCC to AGND with a 4.7 µF capacitor.

A UVLO circuit is also included in the regulator. When INTVCC

< 3.8 V, the two switching regulators and the linear regulator

controller are shut down. The UVLO hysteresis voltage is about

120 mV. The internal LDO has a built-in fold-back current

limit, so that it will be protected if a short circuit is applied to

the 5 V output.

If AUXVCC is higher than 4.75 V, and both the 5 V and 3.3 V

switching regulators are in PSV mode, an internal switch will

connect INTVCC to AUXVCC, while simultaneously turning

off the internal LDO. AUXVCC can be tied to either the 5 V

switching regulator output or a separate 5 V voltage source. By

doing this, the power loss across the internal LDO is eliminated,

and the total efficiency in PSV mode is improved.

When AUXVCC = GND, this automatic power switchover fea-

ture will be disabled.

Internal Reference (REF)

The ADP3020 contains a precision 1.2 V bandgap reference.

Bypass REF to AGND with a 1 nF ceramic capacitor. The ref-

erence is intended for internal use only. An external voltage

buffer is needed if the reference is used for another purpose.

Boost High Side Gate Drive Supply (BST)

The gate drive voltage for the high-side N-channel MOSFETs is

generated by a flying-capacitor boost circuit. The boost capacitor

connected between BST and SW is charged from the INTVCC

supply. Use only small-signal diodes for the boost circuit.

–10–

REV. 0