M80C286 データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

M80C286 Datasheet PDF : 60 Pages

| |||

M80C286

SINGLE STEP INTERRUPT

The M80C286 has an internal interrupt that allows

programs to execute one instruction at a time It is

called the single step interrupt and is controlled by

the single step flag bit (TF) in the flag word Once

this bit is set an internal single step interrupt will

occur after the next instruction has been executed

The interrupt clears the TF bit and uses an internally

supplied vector of 1 The IRET instruction is used to

set the TF bit and transfer control to the next instruc-

tion to be single stepped

Interrupt Priorities

When simultaneous interrupt requests occur they

are processed in a fixed order as shown in Table 5

Interrupt processing involves saving the flags return

address and setting CS IP to point at the first in-

struction of the interrupt handler If other interrupts

remain enabled they are processed before the first

instruction of the current interrupt handler is execut-

ed The last interrupt processed is therefore the first

one serviced

Table 5 Interrupt Processing Order

Order

Interrupt

1

Instruction exception

2

Single step

3

NMI

4

Processor extension segment overrun

5

INTR

6

INT instruction

Initialization and Processor Reset

Processor initialization or start up is accomplished

by driving the RESET input pin HIGH RESET forces

the M80C286 to terminate all execution and local

bus activity No instruction or bus activity will occur

as long as RESET is active After RESET becomes

inactive and an internal processing interval elapses

the M80C286 begins execution in real address

mode with the instruction at physical location

FFFFF0(H) RESET also sets some registers to pre-

defined values as shown in Table 6

Table 6 M80C286 Initial Register State after RESET

Flag word

Machine Status Word

Instruction pointer

Code segment

Data segment

Extra segment

Stack segment

0002(H)

FFF0(H)

FFF0(H)

F000(H)

0000(H)

0000(H)

0000(H)

HOLD must not be active during the time from the

leading edge of RESET to 34 CLKs after the trailing

edge of RESET

Machine Status Word Description

The machine status word (MSW) records when a

task switch takes place and controls the operating

mode of the M80C286 It is a 16-bit register of which

the lower four bits are used One bit places the CPU

into protected mode while the other three bits as

shown in Table 7 control the processor extension

interface After RESET this register contains

FFF0(H) which places the M80C286 in M8086 real

address mode

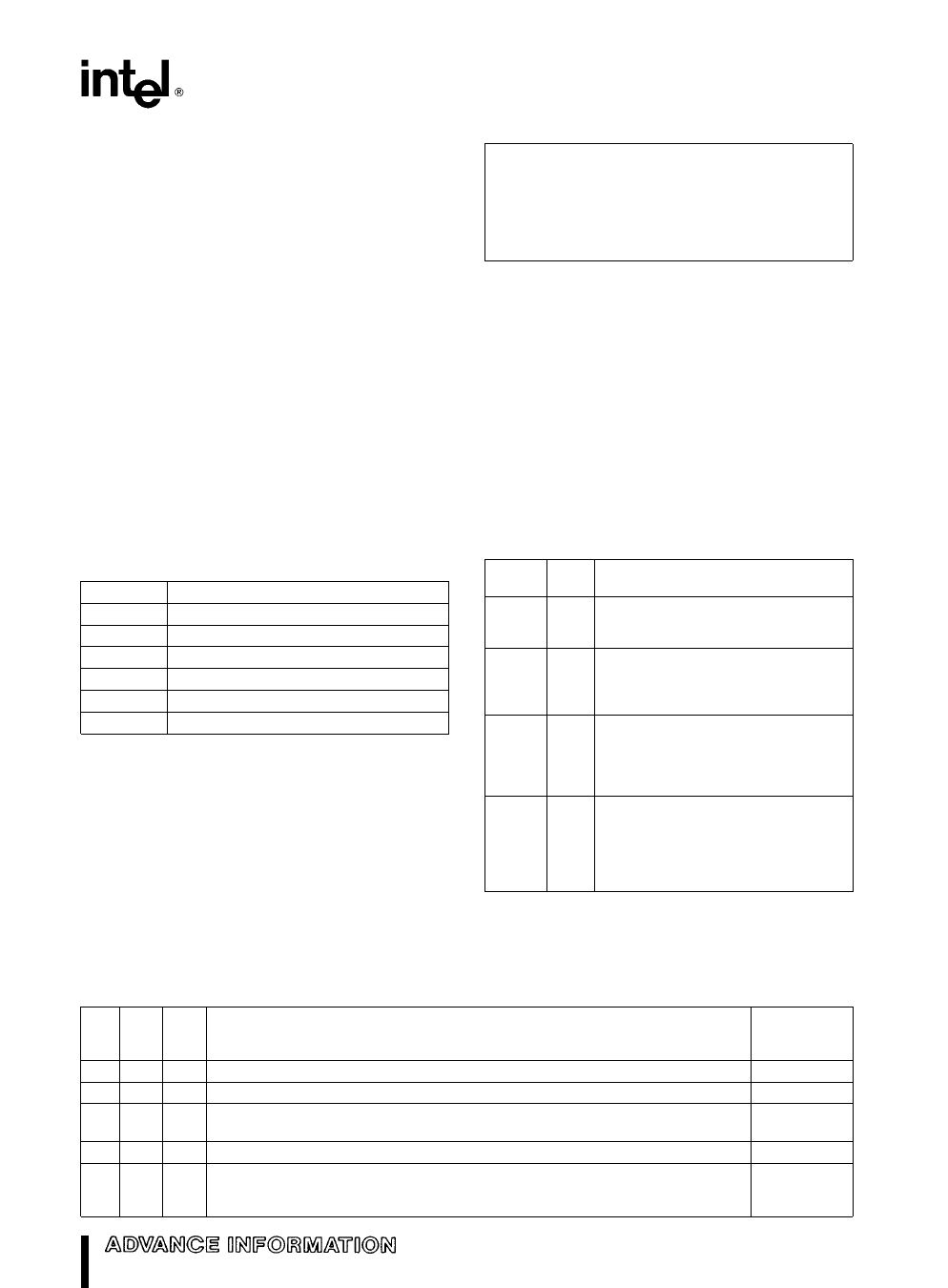

Table 7 MSW Bit Functions

Bit

Position

Name

Function

0

PE Protected mode enable places the

M80C286 into protected mode and

cannot be cleared except by RESET

1

MP Monitor processor extension allows

WAIT instructions to cause a processor

extension not present exception

(number 7)

2

EM Emulate processor extension causes a

processor extension not present

exception (number 7) on ESC

instructions to allow emulating a

processor extension

3

TS Task switched indicates the next

instruction using a processor extension

will cause exception 7 allowing software

to test whether the current processor

extension context belongs to the current

task

The LMSW and SMSW instructions can load and

store the MSW in real address mode The recom-

mended use of TS EM and MP is shown in Table 8

Table 8 Recommended MSW Encodings For Processor Extension Control

TS MP EM

Recommended Use

Instructions

Causing

Exception 7

0 0 0 Initial encoding after RESET M80C286 operation is identical to M8086 88

None

0 0 1 No processor extension is available Software will emulate its function

ESC

1 0 1 No processor extension is available Software will emulate its function The current

processor extension context may belong to another task

ESC

0 1 0 A processor extension exists

None

1 1 0 A processor extension exists The current processor extension context may belong to ESC or

another task The Exception 7 on WAIT allows software to test for an error pending

WAIT

from a previous processor extension operation

9