HV7224X データシートの表示(PDF) - Supertex Inc

部品番号

コンポーネント説明

メーカー

HV7224X Datasheet PDF : 7 Pages

| |||

HV7224

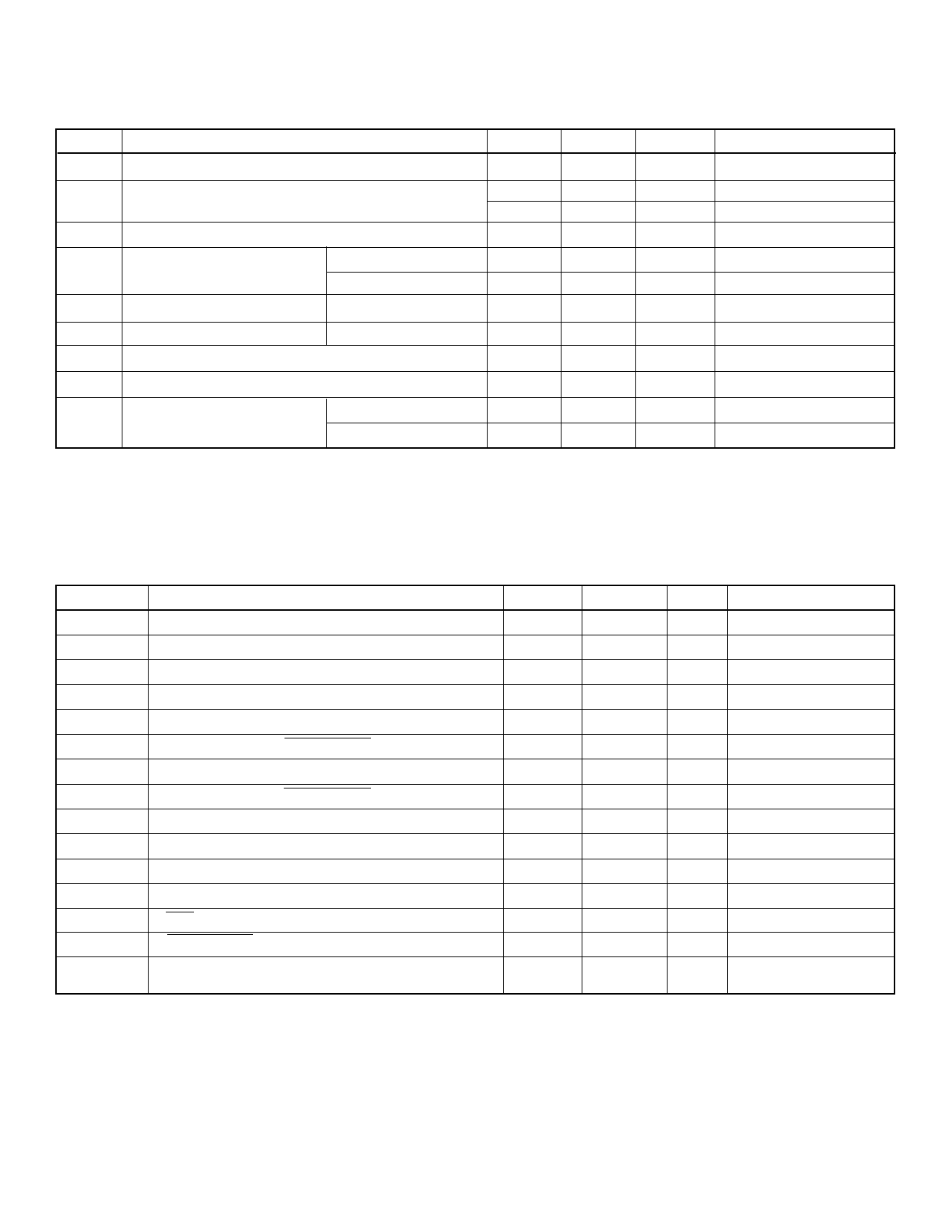

Electrical Characteristics

(over recommended operating conditions of VDD = 5V, VPP = 240V, and TA = 25°C unless noted)

DC Characteristics

Symbol

Parameter

Min

Max

Units

Conditions

IDD

VDD supply current

IPP

High voltage supply current

IDDQ Quiescent VDD supply current

VOH High-level output

HVOUT

Data out

VOL Low-level output

HVOUT

Data out

IIH

High-level logic input current

IIL

Low-level logic input current

ISAT Saturation current HVOUT

P-Ch

N-Ch

10

mA

fCLK = 3MHz

2.0

mA

Outputs low or High-Z

4.0

mA

One Output High1

100

µA

All VIN = GND or VDD

190

V

IO= -70mA

4.5

V

IO= -100µA

50

V

IO= 70mA

0.5

V

IO= 100µA

1.0

µA

VIH = VDD

-1.0

µA

VIL = 0V

-80

mA

75

mA

Note:

1. Only one output can be turned on at a time.

AC Characteristics

Symbol

Parameter

Min

Max

Units Conditions

fCLK

tW (H/L)

tSUD

tHD

tSUC

tSUE

tHC

tHE

tDHL*

tDLH*

tONF

tONR

tPOW

tOEW

Clock frequency

Pulse width - clock high or low

Data set-up time before clock rises

Data hold time after clock rises

HVOUT delay from clock rises (Hi-Z to H or L)

HVOUT delay from Output Enable falls

HVOUT delay from clock rises (H or L to Hi-Z)

HVOUT delay from Output Enable rises

Delay time clock to data output falls

Delay time clock to data output rises

HVOUT fall time

HVOUT rise time

POL pulse width

Output Enable pulse width

Slew rate, VPP or GND

3.0

MHz

150

ns

50

ns

50

ns

1.0

µs CL = 330pF // RL = 10kΩ

600

ns CL = 330pF // RL = 10kΩ

2.0

µs CL = 330pF // RL = 10kΩ

600

ns CL = 330pF // RL = 10kΩ

250

ns CL = 15pF

250

ns CL = 15pF

2.0

µs CL = 330pF // RL = 10kΩ

2.0

µs CL = 330pF // RL = 10kΩ

3.0

µs

3.0

µs

45

V/µs One active output driving

4.7nF load

* The delay is measured from the trailing edge of the clock but the data is triggered by the rising edge of the clock. There is an internal delay for the data output which is

equal to tWH. Therefore the delay is measured from the trailing edge of the clock.

2