MSC8122(2006) データシートの表示(PDF) - Freescale Semiconductor

部品番号

コンポーネント説明

メーカー

MSC8122 Datasheet PDF : 88 Pages

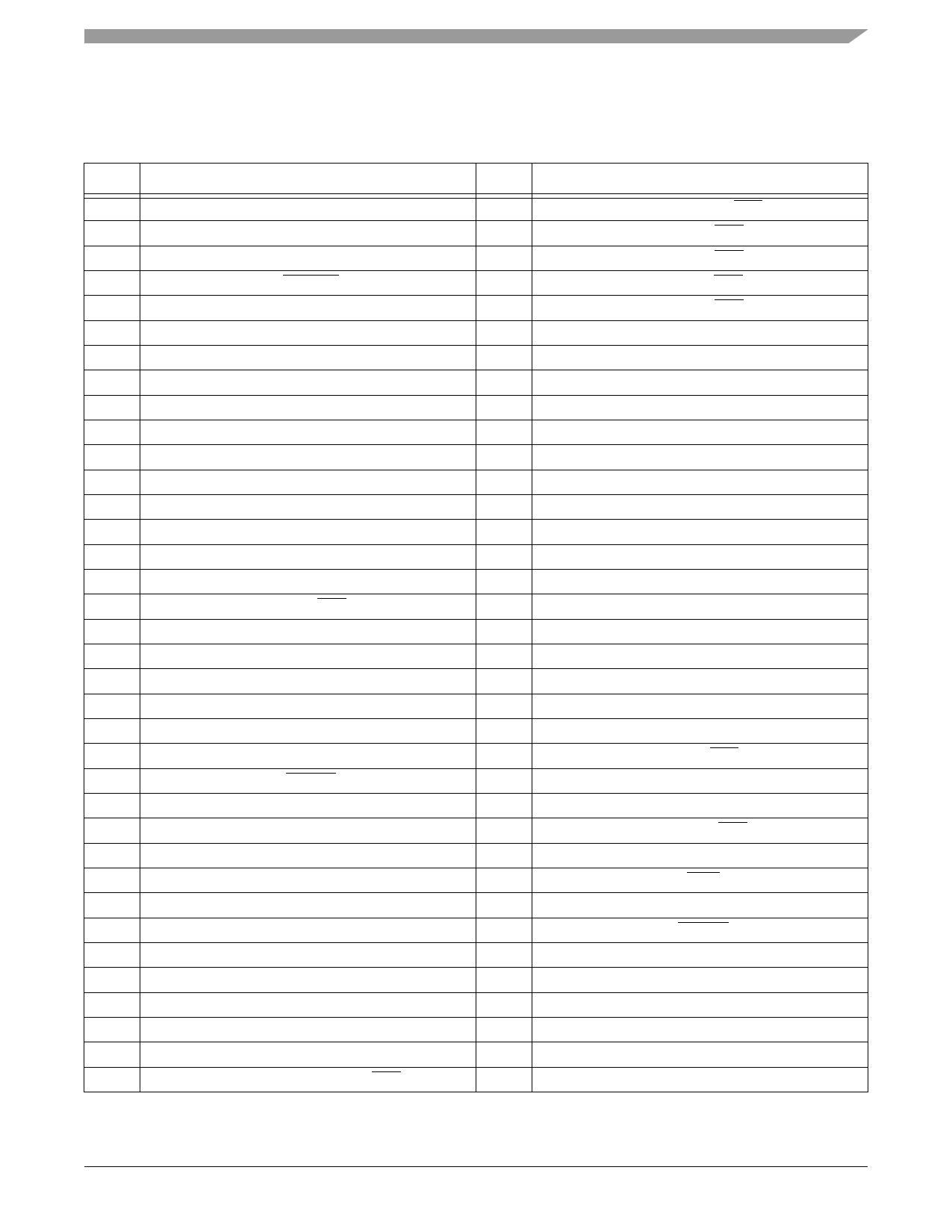

| |||

Features

Feature

UART

General-Purpose I/O

(GPIO) Port

I2C Software Module

Timers

Hardware

Semaphores

Global Interrupt

Controller (GIC)

Reduced Power

Dissipation

Packaging

Real-Time Operating

System (RTOS)

Description

• Two signals for transmit data and receive data.

• No clock, asynchronous mode.

• Can be serviced either by the SC140 DSP cores or an external host on the system bus or the DSI.

• Full-duplex operation.

• Standard mark/space non-return-to-zero (NRZ) format.

• 13-bit baud rate selection.

• Programmable 8-bit or 9-bit data format.

• Separately enabled transmitter and receiver.

• Programmable transmitter output polarity.

• Two receiver wake-up methods:

— Idle line wake-up.

— Address mark wake-up.

• Separate receiver and transmitter interrupt requests.

• Nine flags, the first five can generate interrupt request:

— Transmitter empty.

— Transmission complete.

— Receiver full.

— Idle receiver input.

— Receiver overrun.

— Receiver active.

— Noise error.

— Framing error.

— Parity error.

• Receiver framing error detection.

• Hardware parity checking.

• 1/16 bit-time noise detection.

• Maximum bit rate 6.25 Mbps.

• Single-wire and loop operations.

• 32 bidirectional signal lines that either serve the peripherals or act as programmable I/O ports.

• Each port can be programmed separately to serve up to two dedicated peripherals, and each port supports

open-drain output mode.

• Booting from a serial EEPROM.

• Uses GPIO timing.

Two modules of 16 timers each.

• Cyclic or one-shot.

• Input clock polarity control.

• Interrupt request when counting reaches a programmed threshold.

• Pulse or level interrupts.

• Dynamically updated programmed threshold.

• Read counter any time.

Watchdog mode for the timers that connect to the device.

Eight coded hardware semaphores, locked by simple write access without need for read-modify-write mechanism.

• Consolidation of chip maskable interrupt and non-maskable interrupt sources and routing to INT_OUT,

NMI_OUT, and to the cores.

• Generation of 32 virtual interrupts (eight to each SC140 core) by a simple write access.

• Generation of virtual NMI (one to each SC140 core) by a simple write access.

• Low power CMOS design.

• Separate power supply for internal logic (1.2 V or 1.1 V) and I/O (3.3 V).

• Low-power standby modes.

• Optimized power management circuitry (instruction-dependent, peripheral-dependent, and mode-dependent).

• 0.8 mm pitch flip-chip plastic ball-grid array (FC-PBGA) with lead-free or lead-bearing spheres.

• 431-connection (ball).

• 20 mm × 20 mm.

The real-time operating system (RTOS) fully supports device architecture (multi-core, memory hierarchy, ICache,

timers, DMA controller, interrupts, peripherals), as follows:

• High-performance and deterministic, delivering predictive response time.

• Optimized to provide low interrupt latency with high data throughput.

• Preemptive and priority-based multitasking.

• Fully interrupt/event driven.

• Small memory footprint.

• Comprehensive set of APIs.

MSC8122 Technical Data, Rev. 13

Freescale Semiconductor

vii