TC7660SEPA723 データシートの表示(PDF) - Microchip Technology

部品番号

コンポーネント説明

メーカー

TC7660SEPA723 Datasheet PDF : 24 Pages

| |||

TC7660S

4.0 DETAILED DESCRIPTION

4.1 Theory of Operation

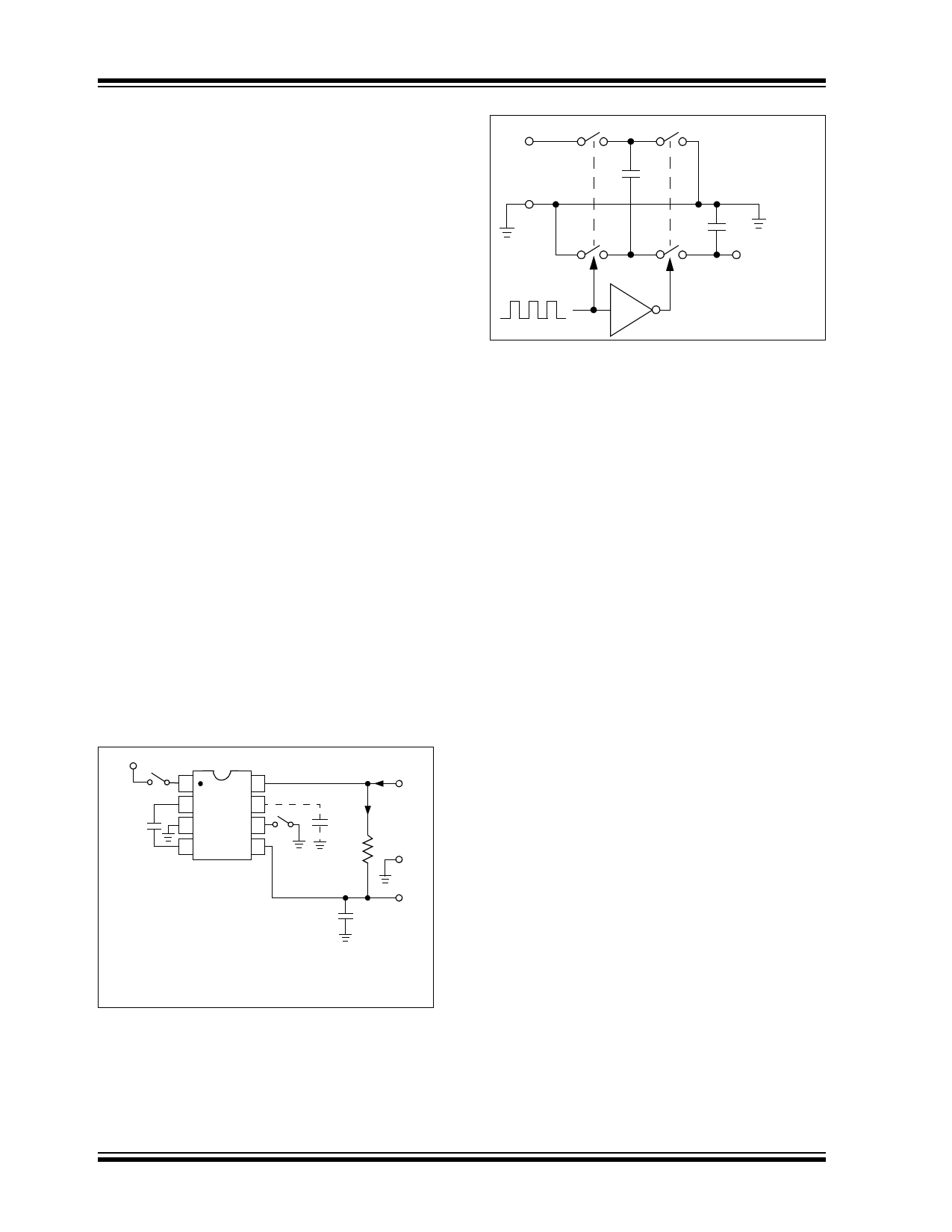

The TC7660S contains all the necessary circuitry to

implement a voltage inverter, with the exception of two

external capacitors, which may be inexpensive 10 µF

polarized electrolytic capacitors. Operation is best

understood by considering Figure 4-2, which shows an

vidoeltaalgizeedV+vofoltar gtheeinhvaelfrtceyr.cCleawpahceintosrwCi1tcihsecshSar1gaenddtoSa3

are closed. (Note that switches S2 and S4 are open

during this half cycle.) During the second half cycle of

operation, switches S2 and S4 are

S3 open, thereby shifting capacitor

Ccl1osneedg,awtivitehlySb1 yaVnd+

tvVho+altvtso.thlCtseh. aCvrohglatearggiseetihsoentnheCtrn2atnrissafneesrxfreaercdrtelfyrdofVmro+mCa1sCns1uetgmoaiCntivg2e, sildyuebcahyl

switches and no load on C2.

The four switches in Figure 4-2 are MOS power

switches; S1 is a P-channel device, and S2, S3 and S4

are N-channel devices. The main difficulty with this

approach is that in integrating the switches, the sub-

strates of S3 and S4 must always remain

reverse-biased with respect to their sources, but not so

much as to degrade their ON resistances. In addition,

at circuit start-up, and under output short circuit condi-

tions (VOUT = V+), the output voltage must be sensed

and the substrate bias adjusted accordingly. Failure to

accomplish this will result in high power losses and

probable device latch-up.

This problem is eliminated in the TC7660S by a logic

network which senses the output voltage (VOUT)

together with the level translators, and switches the

substrates of S3 and S4 to the correct level to maintain

necessary reverse bias.

V+

C1 +

10 µF

1

8

2

7

3 TC7660S 6

4

5

IS

IL

COSC

V+

(+5V)

RL

VOUT

C2

+ 10 µF

Note:

For large values of COSC (>1000 pF), the

values of C1 and C2 should be increased to

100F.

FIGURE 4-1:

TC7660S Test Circuit.

The voltage regulator portion of the TC7660S is an

integral part of the anti-latch-up circuitry. Its inherent

voltage drop can, however, degrade operation at low

voltages.

DS20001467C-page 8

V+

S1

GND S3

S2

+ C1

S4

C2 +

VOUT = -VIN

FIGURE 4-2:

Ideal Charge Pump Inverter.

To improve low-voltage operation, the “LV” pin should

be connected to GND, disabling the regulator. For

supply voltages greater than 3.5V, the LV terminal must

be left open to ensure latch-up-proof operation and

prevent device damage.

4.2 Theoretical Power Efficiency

Considerations

In theory, a capacitive charge pump can approach

100% efficiency if certain conditions are met:

(1) The drive circuitry consumes minimal power.

(2) The output switches have extremely low ON

resistance and virtually no offset.

(3) The impedances of the pump and reservoir

capacitors are negligible at the pump frequency.

The TC7660S approaches these conditions for nega-

tive voltage multiplication if large values of C1 and C2

are used. Energy is lost only in the transfer of charge

between capacitors if a change in voltage occurs. The

energy lost is defined by:

E = 1/2 C1 (V12 – V22)

V1 and V2 are the voltages on C1 during the pump and

transfer cycles. If the impedances of C1 and C2 are rel-

atively high at the pump frequency (refer to Figure 4-2)

compared to the value of RL, there will be a substantial

difference in voltages V1 and V2. Therefore, it is desir-

able not only to make C2 as large as possible to

eliminate output voltage ripple, but also to employ a

correspondingly large value for C1 in order to achieve

maximum efficiency of operation.

4.3 Dos and Don'ts

• Do not exceed maximum supply voltages.

• Do not connect the LV terminal to GND for supply

voltages greater than 3.5V.

• Do not short circuit the output to V+ supply for

voltages above 5.5V for extended periods; how-

ever, transient conditions including start-up are

okay.

• When using polarized capacitors in the inverting

mode, the + terminal of C1 must be connected to

pin 2 of the TC7660S and the + terminal of C2

must be connected to GND.

2001-2015 Microchip Technology Inc.