AD9940 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9940 Datasheet PDF : 20 Pages

| |||

Data Sheet

AD9940

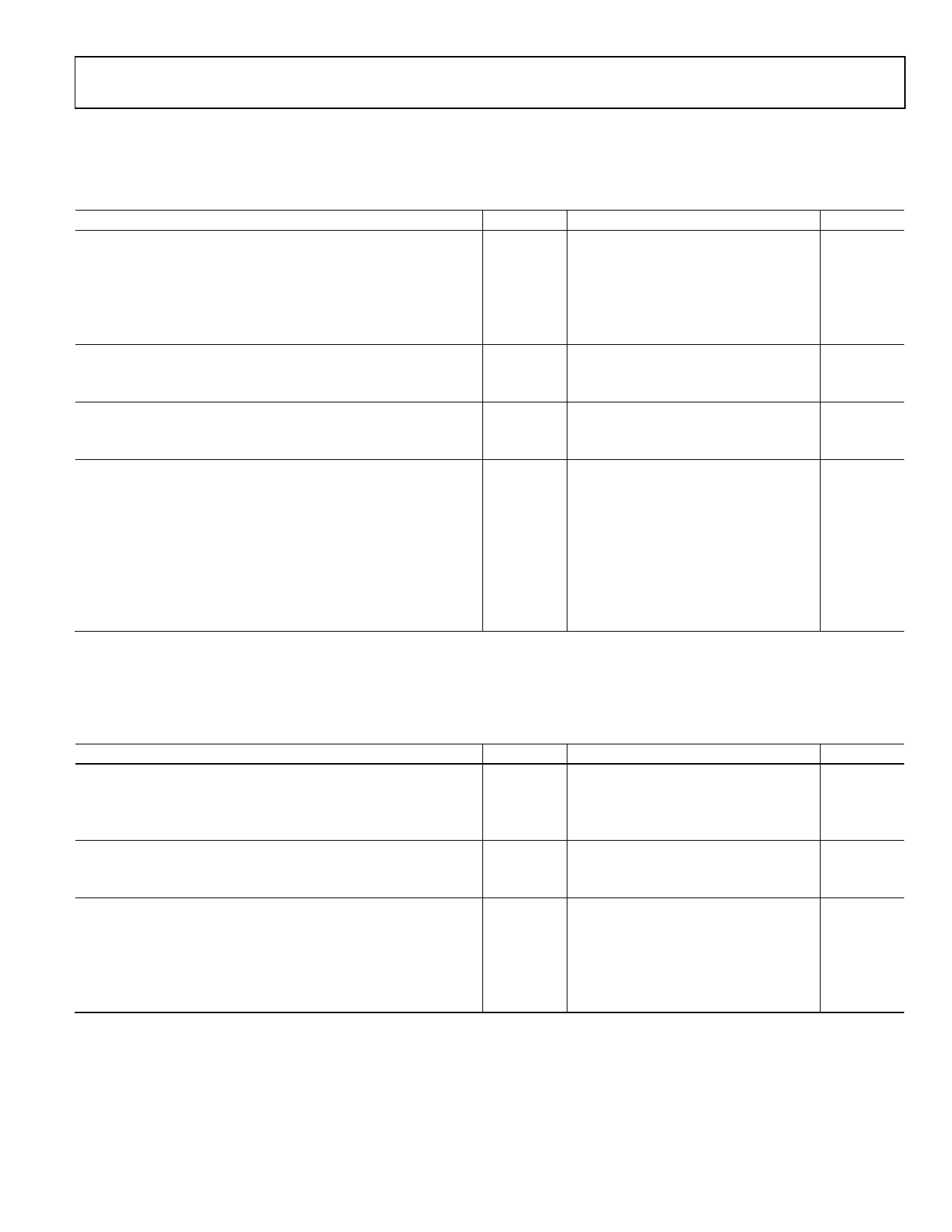

DIGITAL SPECIFICATIONS

TMIN to TMAX, AVDD = DVDD = OVDD = TCVDD = HVDD = RGVDD = 2.7 V, −25°C to +85°C, unless otherwise noted.

Table 3.

Parameter

LOGIC INPUTS

High Level Input Voltage

Low Level Input Voltage

High Level Input Current

Low Level Input Current

Input Capacitance

LOGIC OUTPUTS

High Level Output Voltage, IOH = 2 mA

Low Level Output Voltage, IOL = 2 mA

CLI INPUT

High Level Input Voltage

Low Level Input Voltage

RG-DRIVER AND H-DRIVER OUTPUTS (powered by HVDD, RGVDD)

High Level Output Voltage (at max output current)

Low Level Output Voltage (at max output current)

Maximum Output Current (programmable)

H-Driver (per output)

RG-Driver, HL-Driver

Maximum Load Capacitance

H-Driver (per output)

RG-Driver, HL-Driver

Symbol

VIH

VIL

IIH

IIL

CIN

VOH

VOL

VIH–CLI

VIL–CLI

VOH

VOL

Min

Typ

2.1

10

10

10

2.2

1.85

VDD − 0.5

64

15

100

50

Max

Unit

V

0.6

V

µA

µA

pF

V

0.5

V

V

0.85

V

V

0.5

V

mA

mA

pF

pF

TIMING SPECIFICATIONS (SLAVE TIMING MODE)

See Figure 10 for Timing Diagram.

Table 4.

Parameter

MASTER CLOCK (CLI)

CLI Clock Period

CLI High Pulse Width

Internal Delay from CLI to First Tap

SAMPLE CLOCKS

SHP Rising to SHD Rising

ADCLK Edge Placement for AD9941

SERIAL INTERFACE

Maximum SCK Frequency

SL to SCK Setup Time

SCK to SL Hold Time

SDATA Valid to SCK Rising Edge Setup

SCK Rising Edge to SDATA Valid Hold

Symbol

Min

Typ

Max

Unit

TCLI

18

ns

TADC

9

ns

TCLIDLY

6

ns

TS1

7.4

9

ns

TREC

3

ns

fSCLK

10

tLS

10

tLH

10

tDS

10

tDH

10

MHz

ns

ns

ns

ns

Rev. A | Page 5 of 20