ADM8693ANZ データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

ADM8693ANZ Datasheet PDF : 20 Pages

| |||

ADM8690/ADM8691/ADM8692/ADM8693/ADM8695

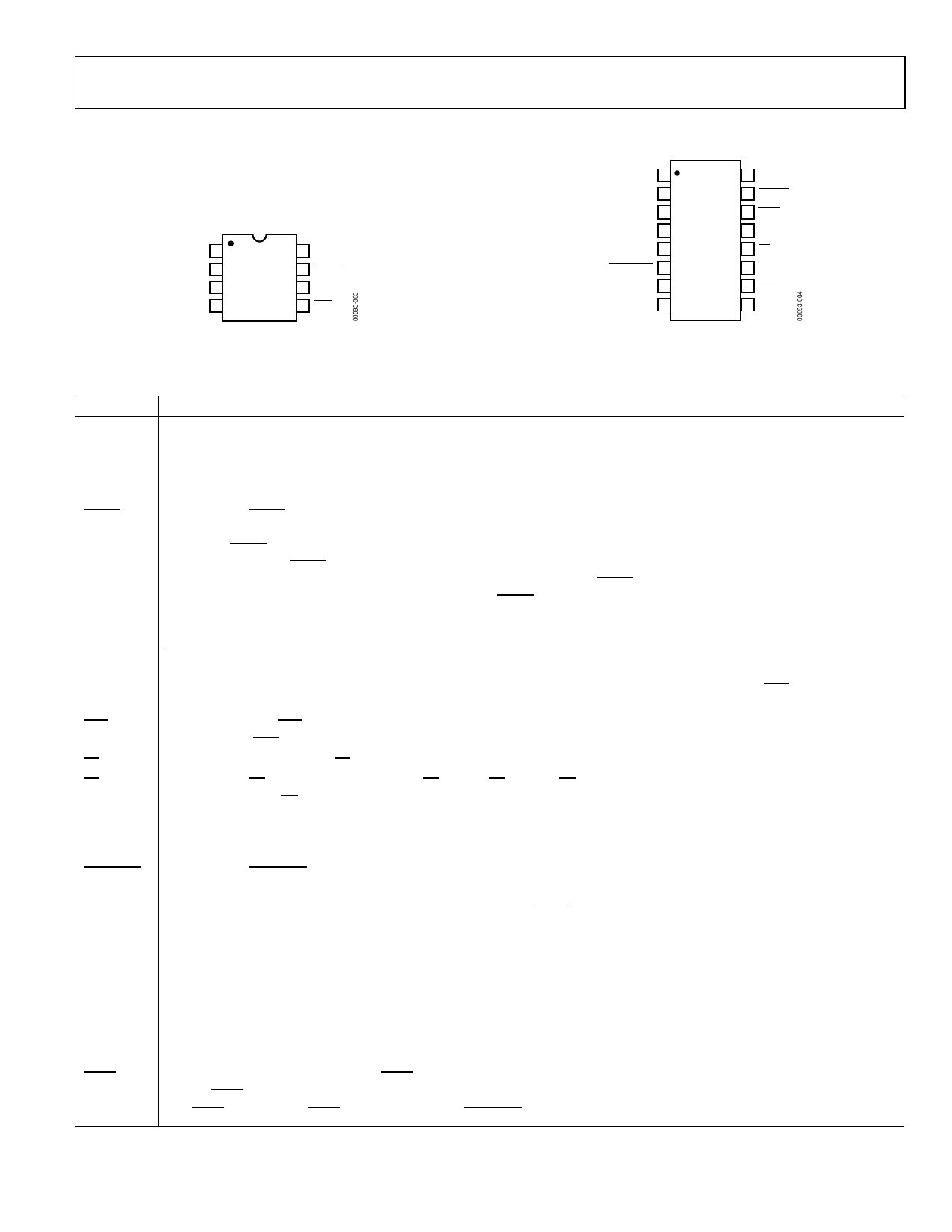

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

VOUT 1

VCC 2

GND 3

PFI 4

ADM8690/

ADM8692

TOP VIEW

(Not to Scale)

8 VBATT

7 RESET

6 WDI

5 PFO

Figure 3. ADM8690 and ADM8692,

Pin Configuration

VBATT 1

16 RESET

VOUT 2

15 RESET

VCC 3 ADM8691/ 14 WDO

ADM8693/

GND 4 ADM8695 13 CEIN

BATT ON 5 TOP VIEW 12 CEOUT

LOW LINE

6

(Not to Scale)

11 WDI

OSC IN 7

10 PFO

OSC SEL 8

9 PFI

Figure 4. ADM8691, ADM8693, and ADM8695

Pin Configuration

Table 4. Pin Function Descriptions

Mnemonic Function

VCC

VBATT

VOUT

GND

Power Supply Input. 5 V nominal.

Backup Battery Input.

Output Voltage. VCC or VBATT is internally switched to VOUT, depending on which is at the highest potential. VOUT can supply up to

100 mA to power CMOS RAM. Connect VOUT to VCC if VOUT and VBATT are not used.

Ground. This is the 0 V ground reference for all signals.

RESET

Logic Output. RESET goes low if VCC falls below the reset threshold, or the watchdog timer is not serviced within its timeout

period. The reset threshold is typically 4.65 V for the ADM8690/ADM8691/ADM8695 and 4.4 V for the ADM8692 and

ADM8693. RESET remains low for 50 ms (ADM8690/ADM8691/ADM8692/ADM8693) or 200 ms (ADM8695) after VCC returns

above the threshold. RESET also goes low for 50 ms (ADM8690/ADM8691/ADM8692/ADM8693) or 200 ms (ADM8695) if the

watchdog timer is enabled but not serviced within its timeout period. The RESET pulse width can be adjusted on the

ADM8691/ADM8693/ADM8695, as shown in Table 5. The RESET output has an internal 3 µA pull-up, and can either connect to

an open collector reset bus or directly drive a CMOS gate without an external pull-up resistor.

WDI

Watchdog Input. WDI is a three-level input. If WDI remains either high or low for longer than the watchdog timeout period,

RESET pulses low and WDO goes low. The timer resets with each transition on the WDI line. The watchdog timer can be

disabled if WDI is left floating or is driven to midsupply.

PFI

PFO

CEIN

CEOUT

BATT ON

LOW LINE

Power-Fail Input. PFI is the noninverting input to the power-fail comparator. When PFI is less than 1.3 V, PFO goes low.

Connect PFI to GND or VOUT when not used.

Power-Fail Output. PFO is the output of the power-fail comparator. It goes low when PFI is less than 1.3 V. The comparator is

turned off and PFO goes low when VCC is below VBATT.

Logic Input. The input to the CE gating circuit. When not in use, connect this pin to GND or VOUT.

Logic Output. CEOUT is a gated version of the CEIN signal. CEOUT tracks CEIN when VCC is above the reset threshold. If VCC is below

the reset threshold, CEOUT is forced high. See Figure 21 and Figure 22.

Logic Output. BATT ON goes high when VOUT is internally switched to the VBATT input. It goes low when VOUT is internally

switched to VCC. The output typically sinks 35 mA and can directly drive the base of an external PNP transistor to increase the

output current above the 100 mA rating of VOUT.

Logic Output. LOW LINE goes low when VCC falls below the reset threshold. It returns high as soon as VCC rises above the reset

threshold.

RESET

Logic Output. RESET is an active high output. It is the inverse of RESET.

OSC SEL

Logic Oscillator Select Input. When OSC SEL is unconnected (floating) or driven high, the internal oscillator sets the reset

active time and watchdog timeout period. When OSC SEL is low, the external oscillator input, OSC IN, is enabled. OSC SEL has

a 3 µA internal pull-up (see Table 5).

OSC IN

Oscillator Logic Input. With OSC SEL low, OSC IN can be driven by an external clock signal or an external capacitor can be

connected between OSC IN and GND. This sets both the reset active pulse timing and the watchdog timeout period (see

Table 5 and Figure 17, Figure 18, Figure 19, and Figure 20). With OSC SEL high or floating, the internal oscillator is enabled and

the reset active time is fixed at 50 ms typical (ADM8691/ADM8693) or 200 ms typical (ADM8695). In this mode, the OSC IN pin

selects between fast (100 ms) and slow (1.6 s) watchdog timeout periods. In both modes, the timeout period immediately

after a reset is 1.6 s typical.

WDO

Logic Output. The watchdog output, WDO, goes low if WDI remains either high or low for longer than the watchdog timeout

period. WDO is set high by the next transition at WDI. If WDI is unconnected or at midsupply, the watchdog timer is disabled

and WDO remains high. WDO also goes high when LOW LINE goes low.

Rev. B | Page 7 of 20