AT88SA10HS(2009) データシートの表示(PDF) - Atmel Corporation

部品番号

コンポーネント説明

メーカー

AT88SA10HS Datasheet PDF : 23 Pages

| |||

3.1.

IO Flags

The system is always the bus master, so before any IO transaction, the system must send an 8 bit flag to the chip to

indicate the IO operation that is to be performed, as follows:

Value

0x66

0x99

0xCC

Name

Command

Transmit

Sleep

Meaning

After this flag, the system starts sending a command block to the chip. The first bit of the

block can follow immediately after the last bit of the flag.

After a turn-around delay, the chip will start transmitting the response for a previously

transmitted command block.

Upon receipt of a sleep flag, the chip will enter a low power mode until the next wake token

is received.

All other values are reserved and will be ignored. Note that the values of flag for the AT88SA10HSS host are different

from that of the two clients, the AT88SA100S and AT88SA102S. In this manner, both the AT88SA102S (or

AT88SA100S) and AT88SA10HSS can share the same communications pin on the system controller. While the

AT88SA10HS will wake up when communications are sent to the client, it will ignore all such transactions.

It is possible that data values transmitted to a client authentication chip (either theAT88SS100S or the AT88SA102S)

could be interpreted by the AT88SA10HS host chip as a legal transmit flag. In this case there could be a bus conflict as

both the host and client chips drive the signal wire at the same time. To prevent this, the PauseShort command should

be used to prevent the AT88SA10HS host chip from looking at the signal wire during any IO transaction to the client.

3.1.1. Command Timing

After a command flag is transmitted, a command block should be sent to the chip. During parsing of the parameters

and subsequent execution of a properly received command, the chip will be busy and not respond to transitions on the

signal pin. The delays for these operations are listed in the table below:

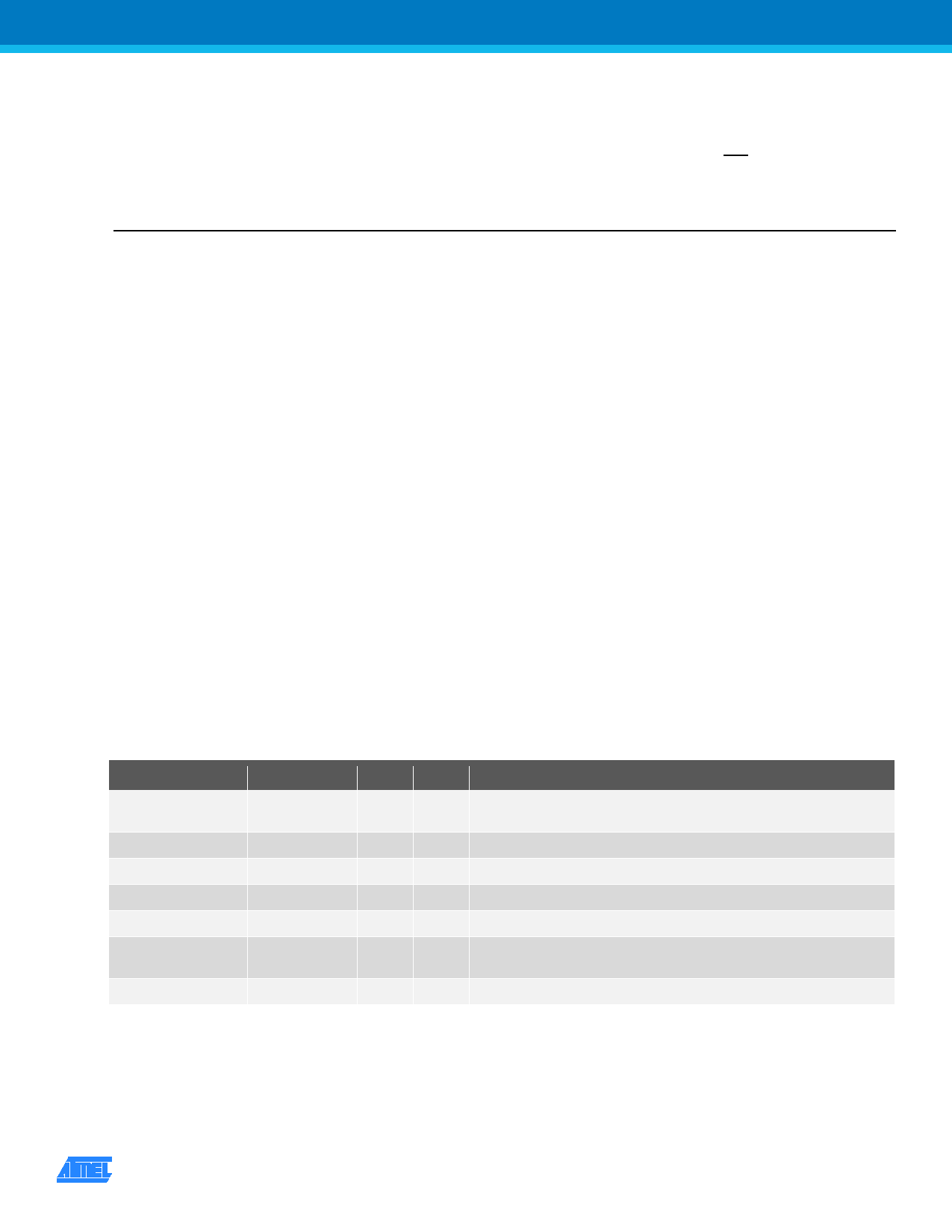

Table 5. Command Timing

Parameter

Symbol

Parsing Delay

t PARSE

Min Max Unit

Notes

0

50

μs

Delay to check CRC and parse opcode and parameters

before an error indication will be available

HostDelay

t EXEC_HOST

15 30 ms Delay to execute any of the 4 HOST commands

MemoryDelay

SecureDelay

PersonalizeDelay

t EXEC_READ

50 100 μs Delay to execute Read command

t EXEC_SECURE

13

26

ms

Max delay to execute BurnSecure command at Vcc > 4.5V.

See Section 4.6 for more details.

t PERSON

7 15 ms Delay to execute GenPersonalizationKey

In this document, t EXEC is used as shorthand for the delay corresponding to whatever command has been sent to the

chip.

8 AT88SA10HS Host Authentication Chip [Preliminary]

8595B–SMEM–09/09