BD2802GU データシートの表示(PDF) - ROHM Semiconductor

部品番号

コンポーネント説明

メーカー

BD2802GU Datasheet PDF : 28 Pages

| |||

BD2802GU

Technical Note

●I2C BUS format

The writing operation is based on the I2C slave standard.

・Slave address

A7 A6 A5

A4

A3

A2

A1 R/W

ADDSEL=L

0

0

1

1

0

1

0

0

ADDSEL=H

0

0

1

1

0

1

1

0

Slave address can be changed with the external terminal ADDSEL.

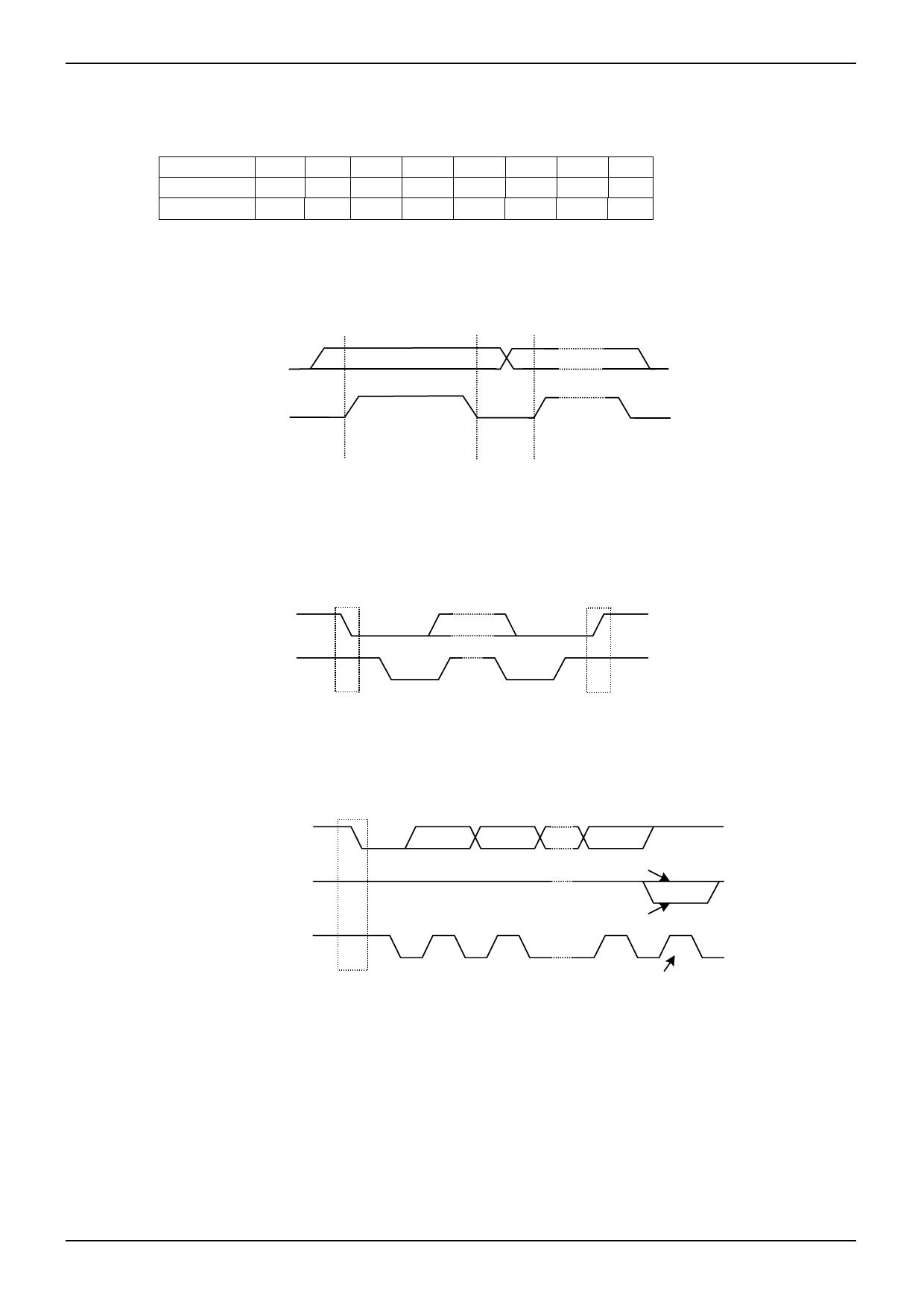

・Bit Transfer

SCL transfers 1-bit data during H. SCL cannot change signal of SDA during H at the time of bit transfer. If SDA changes

while SCL is H, START conditions or STOP conditions will occur and it will be interpreted as a control signal.

SDA

SCL

SDA a state of stability: SDA

Data are effective It can change

・START and STOP condition

When SDA and SCL are H, data is not transferred on the I2C- bus. This condition indicates, if SDA changes from H to L

while SCL has been H, it will become START (S) conditions, and an access start, if SDA changes from L to H while SCL

has been H, it will become STOP (P) conditions and an access end.

SDA

SCL

S

START condition

P

STOP condition

・Acknowledge

It transfers data 8 bits each after the occurrence of START condition. A transmitter opens SDA after transfer 8bits data, and

a receiver returns the acknowledge signal by setting SDA to L.

DATA OUTPUT

BY TRANSMITTER

DATA OUTPUT

BY RECEIVER

SCL

S

1

START condition

not acknowledge

acknowledge

2

8

9

clock pulse for

acknowledgement

www.rohm.com

© 2011 ROHM Co., Ltd. All rights reserved.

7/27

2011.04 - Rev.A