MC-4516DA726F-A10 データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

メーカー

MC-4516DA726F-A10

MC-4516DA726F-A10 Datasheet PDF : 16 Pages

| |||

DATA SHEET

MOS INTEGRATED CIRCUIT

MC-4516DA726

16 M-WORD BY 72-BIT SYNCHRONOUS DYNAMIC RAM MODULE

REGISTERED TYPE

Description

The MC-4516DA726 is a 16,777,216 words by 72 bits synchronous dynamic RAM module on which 18 pieces of

64M SDRAM: µPD4564441 are assembled.

This module provides high density and large quantities of memory in a small space without utilizing the surface-

mounting technology on the printed circuit board.

Decoupling capacitors are mounted on power supply line for noise reduction.

Features

• 16,777,216 words by 72 bits organization (ECC type)

• Clock frequency and access time from CLK

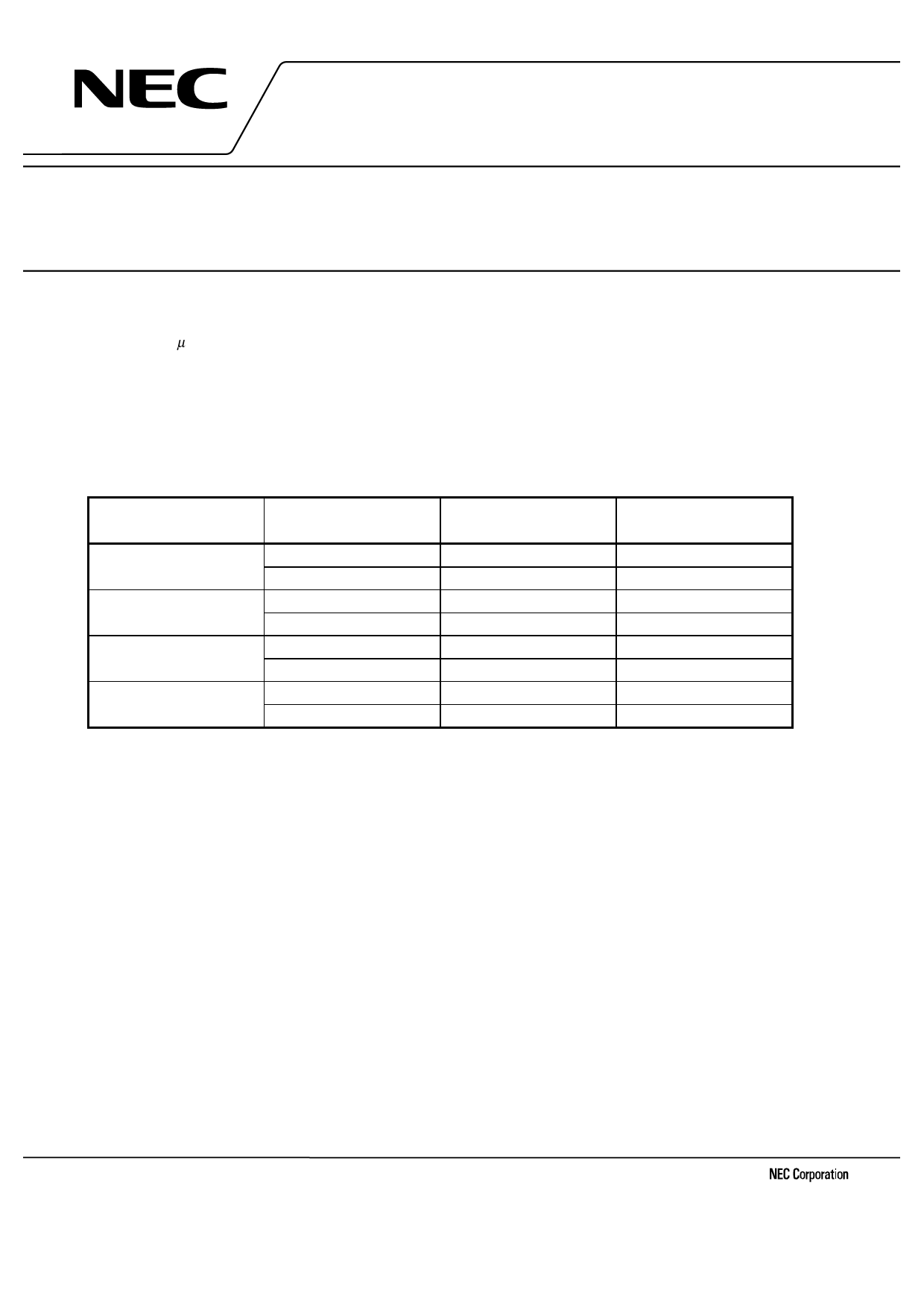

Part number

/CAS latency

MC-4516DA726F-A80

MC-4516DA726F-A10

5 MC-4516DA726LF-A80

5 MC-4516DA726LF-A10

CL = 3

CL = 2

CL = 3

CL = 2

CL = 3

CL = 2

CL = 3

CL = 2

Clock frequency

(MAX.)

125 MHz

100 MHz

100 MHz

77 MHz

125 MHz

100 MHz

100 MHz

77 MHz

Access time from CLK

(MAX.)

6 ns

6 ns

6 ns

7 ns

6 ns

6 ns

6 ns

7 ns

• Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

• Pulsed interface

• Possible to assert random column address in every cycle

• Quad internal banks controlled by BA0 and BA1 (Bank Select)

• Programmable burst-length (1, 2, 4, 8 and Full Page)

• Programmable wrap sequence (Sequential / Interleave)

• Programmable /CAS latency (2, 3)

• Automatic precharge and controlled precharge

• CBR (Auto) refresh and self refresh

• All DQs have 10 Ω ±10 % of series resistor

• Single 3.3 V ±0.3 V power supply

• LVTTL compatible

• 4,096 refresh cycles/64 ms

• Burst termination by Burst Stop command and Precharge command

• 168-pin dual in-line memory module (Pin pitch = 1.27 mm)

• Registered type

• Serial PD

5 • PC100 registered DIMM Rev. 1.0 compliant

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M13203EJ3V0DS00 (3rd edition)

The mark 5 shows major revised points.

©

Date Published March 1999 NS CP(K)

Printed in Japan

1998