SST39VF1601 データシートの表示(PDF) - Silicon Storage Technology

部品番号

コンポーネント説明

メーカー

SST39VF1601 Datasheet PDF : 31 Pages

| |||

16 Mbit / 32 Mbit Multi-Purpose Flash Plus

SST39VF1601 / SST39VF3201

SST39VF1602 / SST39VF3202

Data Sheet

To resume Sector-Erase or Block-Erase operation which has

been suspended the system must issue Erase Resume

command. The operation is executed by issuing one byte

command sequence with Erase Resume command (30H)

at any address in the last Byte sequence.

Chip-Erase Operation

The SST39VF160x/320x provide a Chip-Erase operation,

which allows the user to erase the entire memory array to

the “1” state. This is useful when the entire device must be

quickly erased.

completion of an internal Write operation, the remaining

data outputs may still be invalid: valid data on the entire

data bus will appear in subsequent successive Read

cycles after an interval of 1 µs. During internal Erase oper-

ation, any attempt to read DQ7 will produce a ‘0’. Once the

internal Erase operation is completed, DQ7 will produce a

‘1’. The Data# Polling is valid after the rising edge of fourth

WE# (or CE#) pulse for Program operation. For Sector-,

Block- or Chip-Erase, the Data# Polling is valid after the

rising edge of sixth WE# (or CE#) pulse. See Figure 7 for

Data# Polling timing diagram and Figure 21 for a flowchart.

The Chip-Erase operation is initiated by executing a six-

byte command sequence with Chip-Erase command

(10H) at address 5555H in the last byte sequence. The

Erase operation begins with the rising edge of the sixth

WE# or CE#, whichever occurs first. During the Erase

operation, the only valid read is Toggle Bit or Data# Polling.

See Table 6 for the command sequence, Figure 10 for tim-

ing diagram, and Figure 24 for the flowchart. Any com-

mands issued during the Chip-Erase operation are

ignored. When WP# is low, any attempt to Chip-Erase will

be ignored. During the command sequence, WP# should

be statically held high or low.

Write Operation Status Detection

The SST39VF160x/320x provide two software means to

detect the completion of a Write (Program or Erase) cycle,

in order to optimize the system write cycle time. The soft-

ware detection includes two status bits: Data# Polling

(DQ7) and Toggle Bit (DQ6). The End-of-Write detection

mode is enabled after the rising edge of WE#, which ini-

tiates the internal Program or Erase operation.

The actual completion of the nonvolatile write is asyn-

chronous with the system; therefore, either a Data# Poll-

ing or Toggle Bit read may be simultaneous with the

completion of the write cycle. If this occurs, the system

may possibly get an erroneous result, i.e., valid data may

appear to conflict with either DQ7 or DQ6. In order to pre-

vent spurious rejection, if an erroneous result occurs, the

software routine should include a loop to read the

accessed location an additional two (2) times. If both

reads are valid, then the device has completed the Write

cycle, otherwise the rejection is valid.

Data# Polling (DQ7)

When the SST39VF160x/320x are in the internal Program

operation, any attempt to read DQ7 will produce the com-

plement of the true data. Once the Program operation is

completed, DQ7 will produce true data. Note that even

though DQ7 may have valid data immediately following the

Toggle Bits (DQ6 and DQ2)

During the internal Program or Erase operation, any con-

secutive attempts to read DQ6 will produce alternating “1”s

and “0”s, i.e., toggling between 1 and 0. When the internal

Program or Erase operation is completed, the DQ6 bit will

stop toggling. The device is then ready for the next opera-

tion. For Sector-, Block-, or Chip-Erase, the toggle bit (DQ6)

is valid after the rising edge of sixth WE# (or CE#) pulse.

DQ6 will be set to “1” if a Read operation is attempted on an

Erase-Suspended Sector/Block. If Program operation is ini-

tiated in a sector/block not selected in Erase-Suspend

mode, DQ6 will toggle.

An additional Toggle Bit is available on DQ2, which can be

used in conjunction with DQ6 to check whether a particular

sector is being actively erased or erase-suspended. Table 1

shows detailed status bits information. The Toggle Bit

(DQ2) is valid after the rising edge of the last WE# (or CE#)

pulse of Write operation. See Figure 8 for Toggle Bit timing

diagram and Figure 21 for a flowchart.

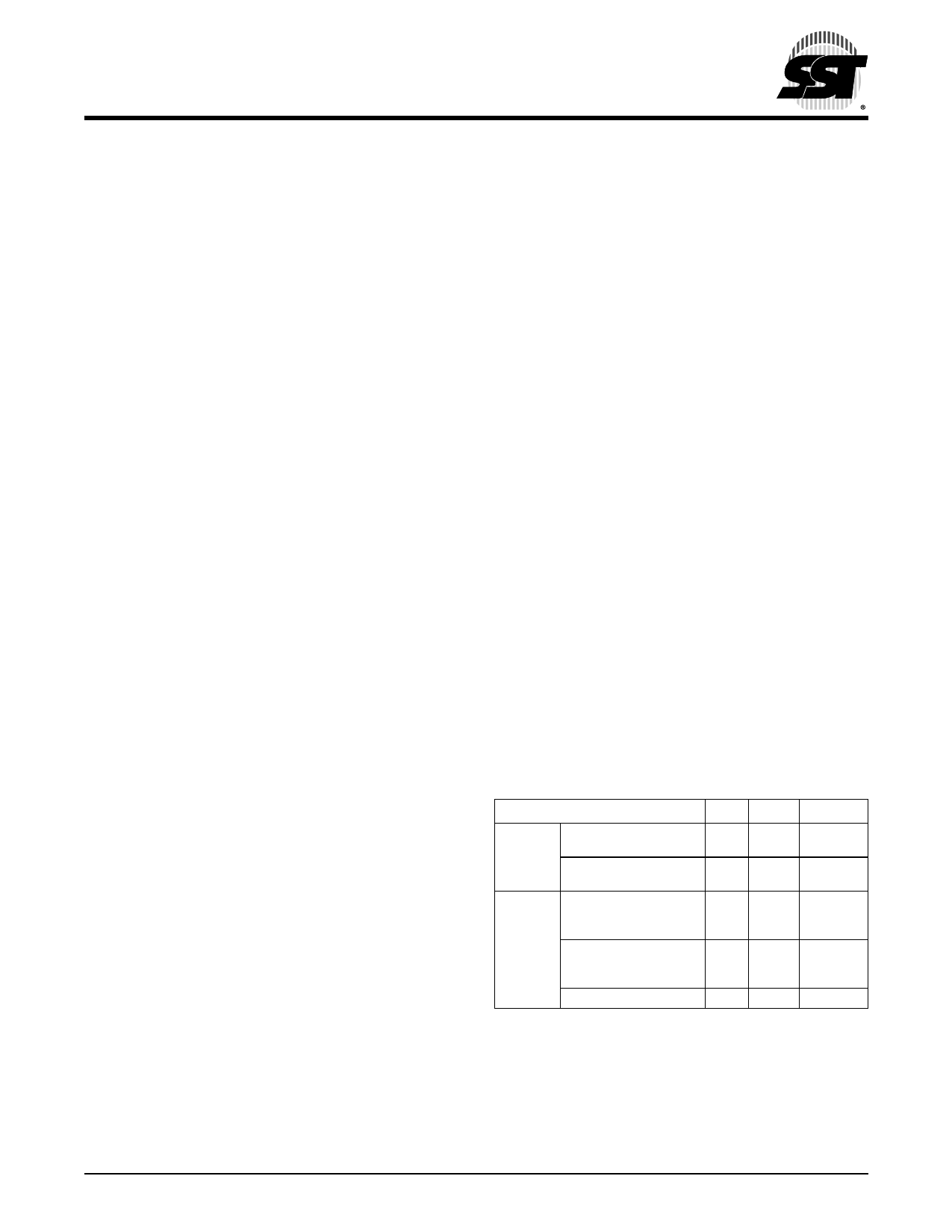

TABLE 1: Write Operation Status

Status

DQ7 DQ6

DQ2

Normal Standard

Operation Program

DQ7# Toggle No Toggle

Standard

Erase

0 Toggle Toggle

Erase- Read from

Suspend Erase-Suspended

Mode

Sector/Block

1

1

Toggle

Read from

Data

Non- Erase-Suspended

Sector/Block

Data

Data

Program

DQ7# Toggle

N/A

T1.0 1223

Note: DQ7 and DQ2 require a valid address when reading

status information.

©2008 Silicon Storage Technology, Inc.

3

S71223-05-000

6/08