SST39VF1601 データシートの表示(PDF) - Silicon Storage Technology

部品番号

コンポーネント説明

メーカー

SST39VF1601 Datasheet PDF : 31 Pages

| |||

16 Mbit / 32 Mbit Multi-Purpose Flash Plus

SST39VF1601 / SST39VF3201

SST39VF1602 / SST39VF3202

Data Sheet

Data Protection

The SST39VF160x/320x provide both hardware and soft-

ware features to protect nonvolatile data from inadvertent

writes.

Hardware Data Protection

Noise/Glitch Protection: A WE# or CE# pulse of less than 5

ns will not initiate a write cycle.

VDD Power Up/Down Detection: The Write operation is

inhibited when VDD is less than 1.5V.

Write Inhibit Mode: Forcing OE# low, CE# high, or WE#

high will inhibit the Write operation. This prevents inadvert-

ent writes during power-up or power-down.

Hardware Block Protection

The SST39VF1602/3202 support top hardware block pro-

tection, which protects the top 32 KWord block of the

device. The SST39VF1601/3201 support bottom hardware

block protection, which protects the bottom 32 KWord block

of the device. The Boot Block address ranges are

described in Table 2. Program and Erase operations are

prevented on the 32 KWord when WP# is low. If WP# is left

floating, it is internally held high via a pull-up resistor, and

the Boot Block is unprotected, enabling Program and

Erase operations on that block.

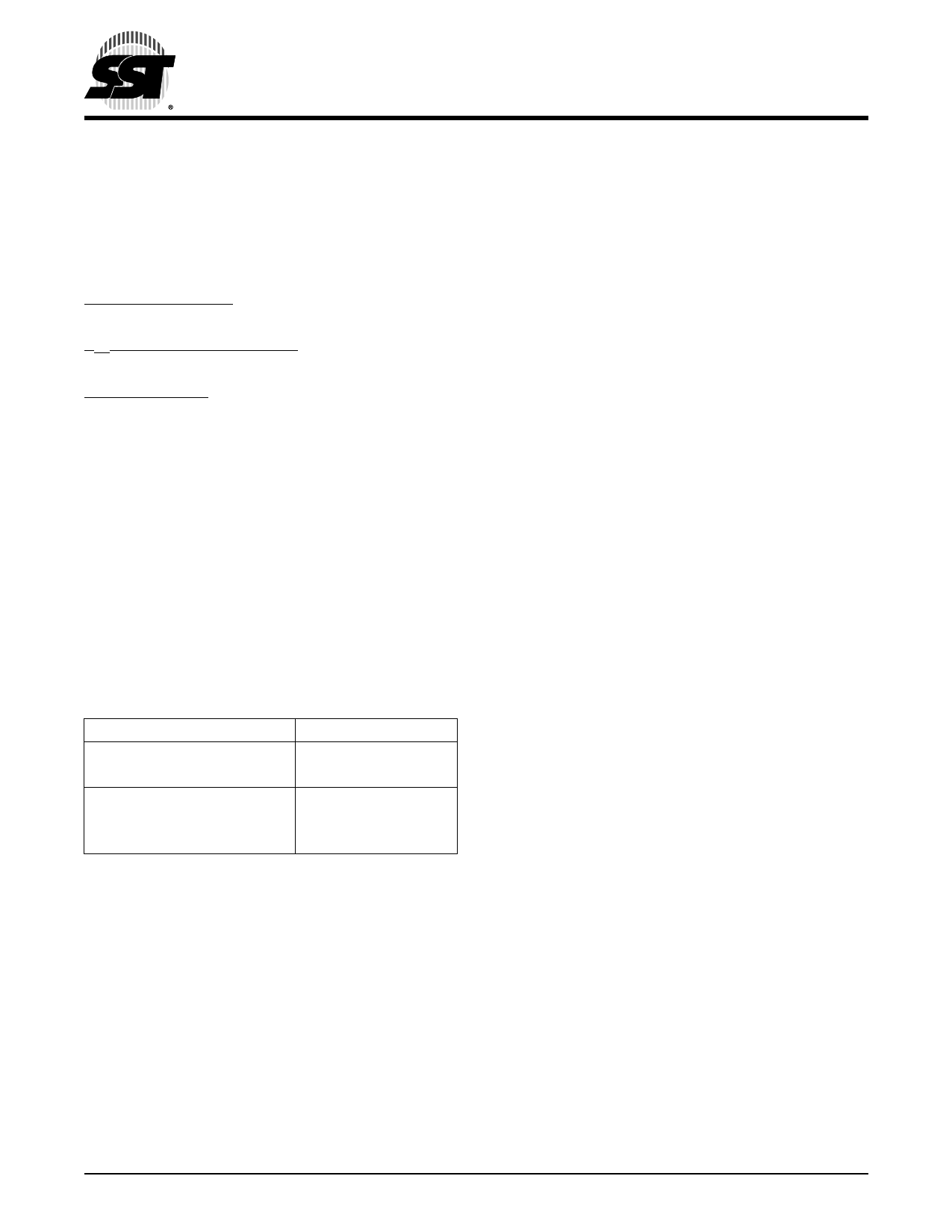

TABLE 2: Boot Block Address Ranges

Product

Address Range

Bottom Boot Block

SST39VF1601/3201

000000H-007FFFH

Top Boot Block

SST39VF1602

SST39VF3202

0F8000H-0FFFFFH

1F8000H-1FFFFFH

T2.0 1223

Hardware Reset (RST#)

The RST# pin provides a hardware method of resetting the

device to read array data. When the RST# pin is held low

for at least TRP, any in-progress operation will terminate and

return to Read mode. When no internal Program/Erase

operation is in progress, a minimum period of TRHR is

required after RST# is driven high before a valid Read can

take place (see Figure 16).

The Erase or Program operation that has been interrupted

needs to be reinitiated after the device resumes normal

operation mode to ensure data integrity.

Software Data Protection (SDP)

The SST39VF160x/320x provide the JEDEC approved

Software Data Protection scheme for all data alteration

operations, i.e., Program and Erase. Any Program opera-

tion requires the inclusion of the three-byte sequence. The

three-byte load sequence is used to initiate the Program

operation, providing optimal protection from inadvertent

Write operations, e.g., during the system power-up or

power-down. Any Erase operation requires the inclusion of

six-byte sequence. These devices are shipped with the

Software Data Protection permanently enabled. See Table

6 for the specific software command codes. During SDP

command sequence, invalid commands will abort the

device to read mode within TRC. The contents of DQ15-DQ8

can be VIL or VIH, but no other value, during any SDP com-

mand sequence.

Common Flash Memory Interface (CFI)

The SST39VF160x/320x also contain the CFI information

to describe the characteristics of the device. In order to

enter the CFI Query mode, the system must write three-

byte sequence, same as product ID entry command with

98H (CFI Query command) to address 5555H in the last

byte sequence. Once the device enters the CFI Query

mode, the system can read CFI data at the addresses

given in Tables 7 through 10. The system must write the

CFI Exit command to return to Read mode from the CFI

Query mode.

©2008 Silicon Storage Technology, Inc.

4

S71223-05-000

6/08