LC75838W データシートの表示(PDF) - SANYO -> Panasonic

部品番号

コンポーネント説明

メーカー

LC75838W Datasheet PDF : 32 Pages

| |||

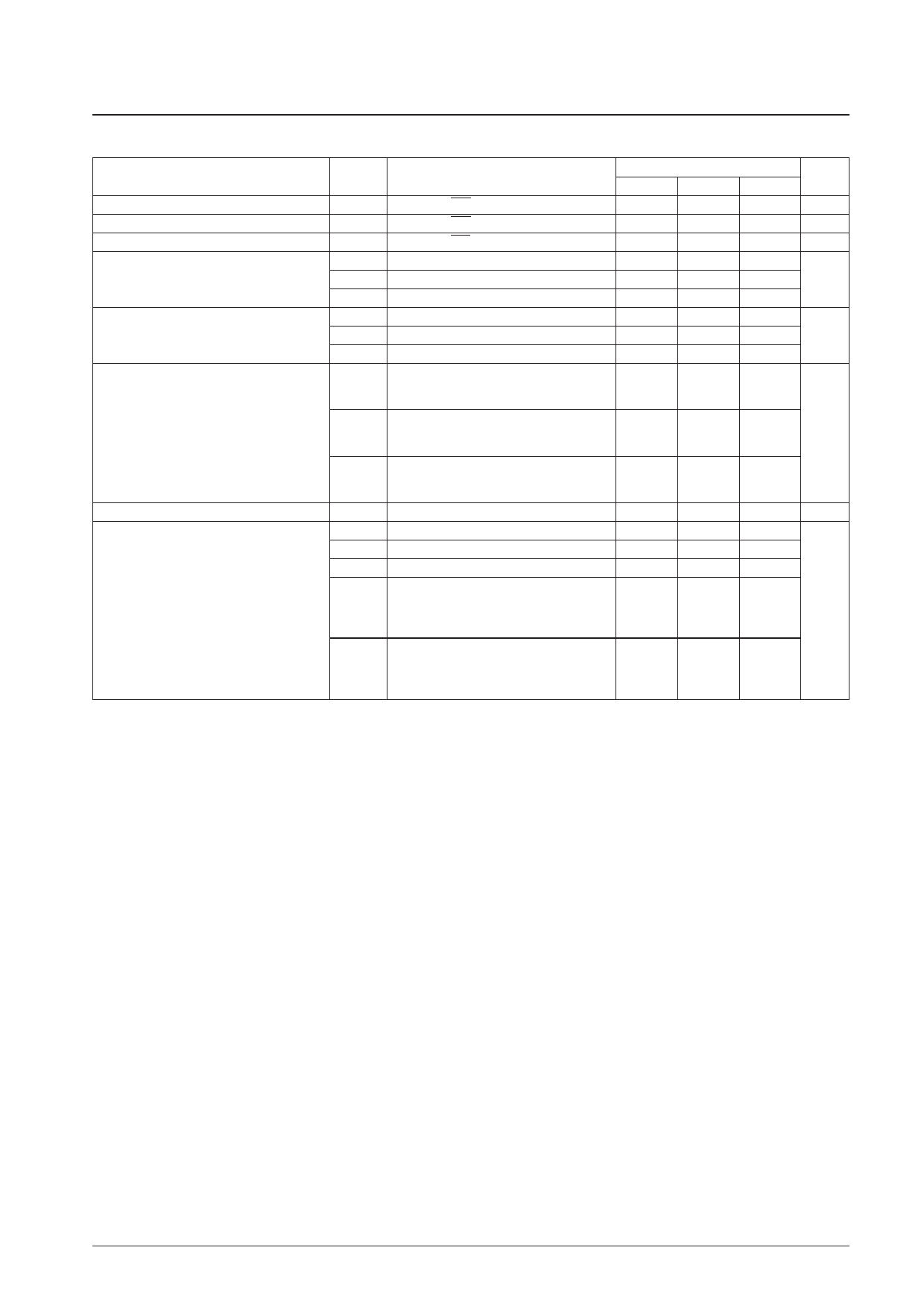

LC75838E, 75838W

Electrical Characteristics for the Allowable Operating Ranges

Parameter

Hysteresis

Input high level current

Input low level current

Output high level voltage

Output low level voltage

Output middle level voltage *1

Oscillator frequency

Current drain

Symbol

Conditions

Ratings

Unit

min

typ

max

VH

IIH

IIL

VOH1

VOH2

VOH3

VOL1

VOL2

VOL3

CE, CL, DI, INH

CE, CL, DI, INH: VI = 6.0 V

CE, CL, DI, INH: VI = 0 V

S1 to S40: IO = –20 µA

COM1 to COM10: IO = –100 µA

P1 to P3: IO = –1 mA

S1 to S40: IO = 20 µA

COM1 to COM10: IO = 100 µA

P1 to P3: IO = 1 mA

VMID1 S1 to S40: IO = ±20 µA

0.1 VDD

V

5.0 µA

–5.0

µA

VLCD0 – 0.6

VLCD0 – 0.6

VDD – 1.0

V

VLCD4 + 0.6

VLCD4 + 0.6

V

1.0

2/4

(VLCD0 – VLCD4)

–0.6

2/4

(VLCD0 – VLCD4)

+0.6

VMID2 COM1 to COM10: IO = ±100 µA

3/4

(VLCD0 – VLCD4)

–0.6

3/4

(VLCD0 – VLCD4)

V

+0.6

VMID3 COM1 to COM10: IO = ±100 µA

1/4

(VLCD0 – VLCD4)

–0.6

1/4

(VLCD0 – VLCD4)

+0.6

fosc OSC: ROSC = 43 kΩ, COSC = 680 pF

40

50

60 kHz

IDD1 VDD : Power saving mode

5

IDD2 VDD: VDD = 6.0 V, outputs open, fosc = 50 kHz

200

400

ILCD1 VLCD : Power saving mode

5

ILCD2

VLCD : VLCD = 11.0 V

Outputs open

fosc = 50 kHz

When the display contrast adjustment circuit is used.

500

1000 µA

ILCD3

VLCD : VLCD = 11.0 V

Outputs open

fosc = 50 kHz

When the display contrast adjustment circuit is not used.

250

500

Note: *1 Excluding the bias voltage generation divider resistor built into VLCD0, VLCD1, VLCD2 , VLCD3, and VLCD4. (See Figure 1.)

No. 6902-4/32