SG1842(2000) データシートの表示(PDF) - Microsemi Corporation

部品番号

コンポーネント説明

メーカー

SG1842 Datasheet PDF : 14 Pages

| |||

PRODUCT DATABOOK 1996/1997

SG1842/SG1843 Series

CURRENT-MODE PWM CONTROLLER

PRODUCTION DATA SHEET

A B S O L U T E M A X I M U M R AT I N G S (Notes 1 & 2)

Supply Voltage (I < 30mA) ............................................................... Self Limiting

CC

Supply Voltage (Low Impedance Source) ........................................................ 30V

Output Current (Peak) ....................................................................................... ±1A

Output Current (Continuous) ....................................................................... 350mA

Output Energy (Capacitive Load) ....................................................................... 5µJ

Analog Inputs (Pins 2, 3) ................................................................. -0.3V to +6.3V

Error Amp Output Sink Current ..................................................................... 10mA

Power Dissipation at T = 25°C (DIL-8) ............................................................ 1W

A

Operating Junction Temperature

Hermetic (J, Y, F, L Packages) ................................................................... 150°C

Plastic (N, M, D, DM Packages) ................................................................ 150°C

Storage Temperature Range .......................................................... -65°C to +150°C

Lead Temperature (Soldering, 10 Seconds) .................................................. 300°C

Note 1. Exceeding these ratings could cause damage to the device.

Note 2. All voltages are with respect to Pin 5. All currents are positive into the specified

terminal.

THERMAL DATA

M PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

N PACKAGE:

95°C/W

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

DM PACKAGE:

65°C/W

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

D PACKAGE:

165°C/W

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

Y PACKAGE:

120°C/W

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

J PACKAGE:

130°C/W

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

F PACKAGE:

80°C/W

THERMAL RESISTANCE-JUNCTION TO CASE, θJC

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

L PACKAGE:

80°C/W

145°C/W

THERMAL RESISTANCE-JUNCTION TO CASE, θJC

THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA

35°C/W

120°C/W

Junction Temperature Calculation: T = T + (P x θ ).

J

A

D

JA

The θ numbers are guidelines for the thermal performance of the device/pc-board

JA

system. All of the above assume no ambient airflow.

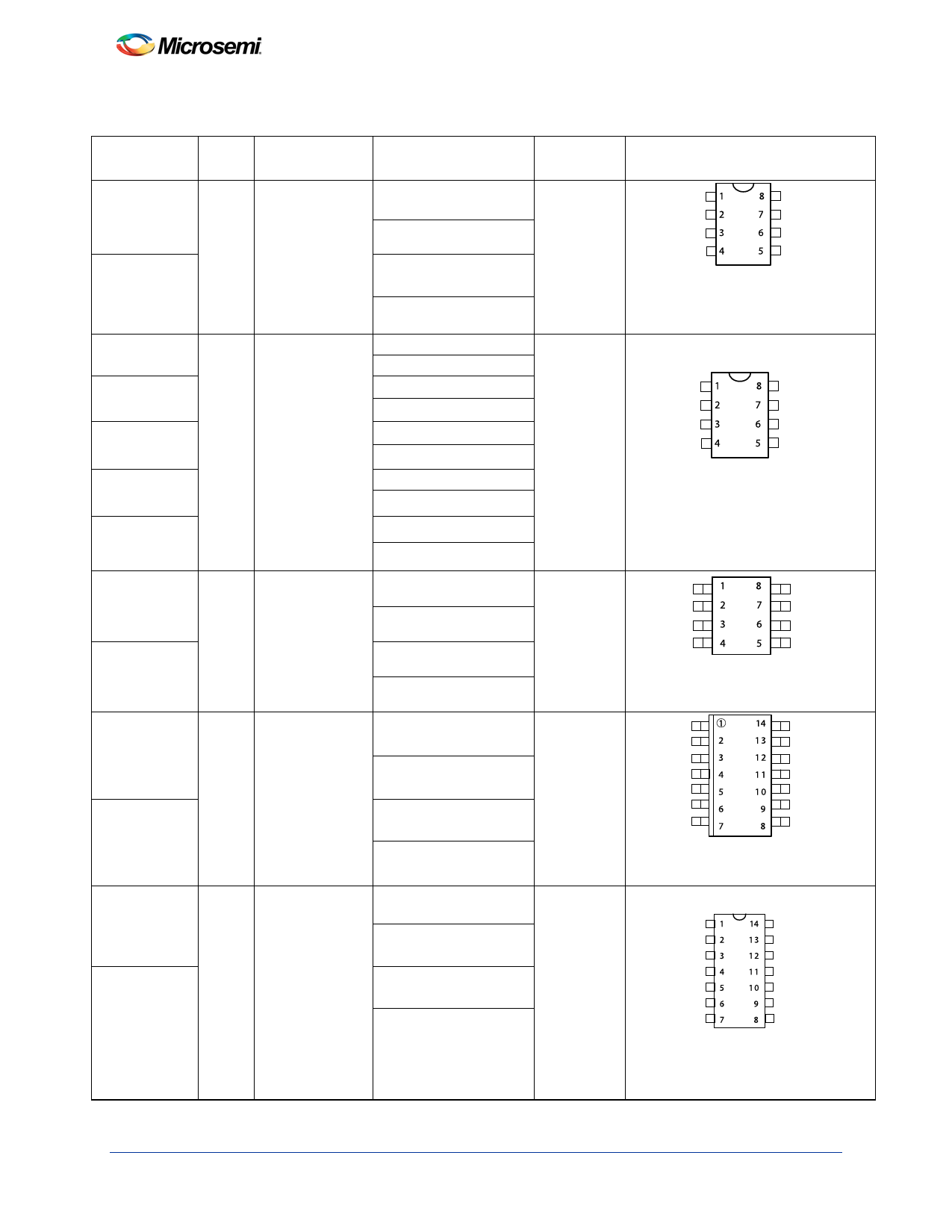

PACKAGE PIN OUTS

COMP 1

VFB

2

ISENSE

3

RT/CT 4

8

VREF

7

VCC

6 OUTPUT

5 GND

M & Y PACKAGE

(Top View)

COMP

VFB

ISENSE

RT/CT

1

8

VREF

2

7

VCC

3

6

OUTPUT

4

5

GND

DM PACKAGE

(Top View)

COMP

N.C.

VFB

N.C.

ISENSE

N.C.

RT/CT

1

14

VREF

2

13

N.C.

3

12

VCC

4

11

VC

5

10

OUTPUT

6

9

GND

7

8

PWR GND

D PACKAGE

(Top View)

COMP 1

14

VREF

N.C. 2 13 N.C.

VFB

3

12

VCC

N.C. 4

11

VC

ISENSE

5

10

OUTPUT

N.C. 6

9 GROUND

RT/CT

7

8 POWER GND

J & N PACKAGE

(Top View)

1. COMP

2. VFB

3. ISENSE

4. RT/CT

5. POWER GND

1

10

2

9

3

8

4

7

5

6

10. VREF

9. VCC

8. VC

7. OUTPUT

6. GND

F PACKAGE

(Top View)

3 2 1 20 19

1. N.C. 11. N.C.

2. COMP 12. GROUND

4

18

3. N.C.

13. N.C.

5

17

4. N.C.

14. N.C.

6

16

5. VFB

6. N.C.

15. OUTPUT

16. N.C.

7

15

7. ISENSE

17. VCC

8

14

8. N.C.

18. N.C.

9. N.C. 19. N.C.

9 10 11 12 13

10. RT/CT 20. VREF

L PACKAGE

(Top View)

2

Copyright © 2000

Rev. 1.6 4/00