AM24LC02 データシートの表示(PDF) - Anachip Corporation

部品番号

コンポーネント説明

メーカー

AM24LC02 Datasheet PDF : 12 Pages

| |||

2-Wire Serial 2K-bits (256 x 8) CMOS Electrically Erasable PROM

Functional Description (Continued)

ATC

AM24LC02

Acknowledge

Each receiving device, when addressed, is obliged

to generate an acknowledge after the reception of

each byte. The master device must generate an

extra clock pulse which is associated with this

acknowledge bit. The device that acknowledges,

has to pull down the SDA line during the

acknowledge clock pulse in such a way that the

SDA line is stable LOW during the HIGH period of

the acknowledge related clock pulse. Of course,

setup and hold times must be taken into account. A

master must signal an end of data to the slave by

not generating an acknowledge bit on the last byte

that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable

the master to generate the STOP condition. (Shown

in Figure 3)

Devices Addressing

After generating a START condition, the bus master

transmits the slave address consisting of a 4-bit

device code (1010) for the AM24LC02, 3-bit device

address (A2 A1 A0) and 1-bit value indicating the

read or write mode. All I2C EEPROMs use and

internal protocol that defines a PAGE BLOCK size of

16K bits. The AM24LC02 contains one 2K-bits

PAGE BLOCK, and the device address bits A0, A1

and A2 are used for determinating which device will

be proceeded in. The eighth bit of slave address

determines if the master device wants to read or

write to the AM24LC02 (Refer to table B).

The AM24LC02 monitors the bus for its

corresponding slave address all the time. It

generates an acknowledge bit if the slave address

was true and it is not in a programming mode.

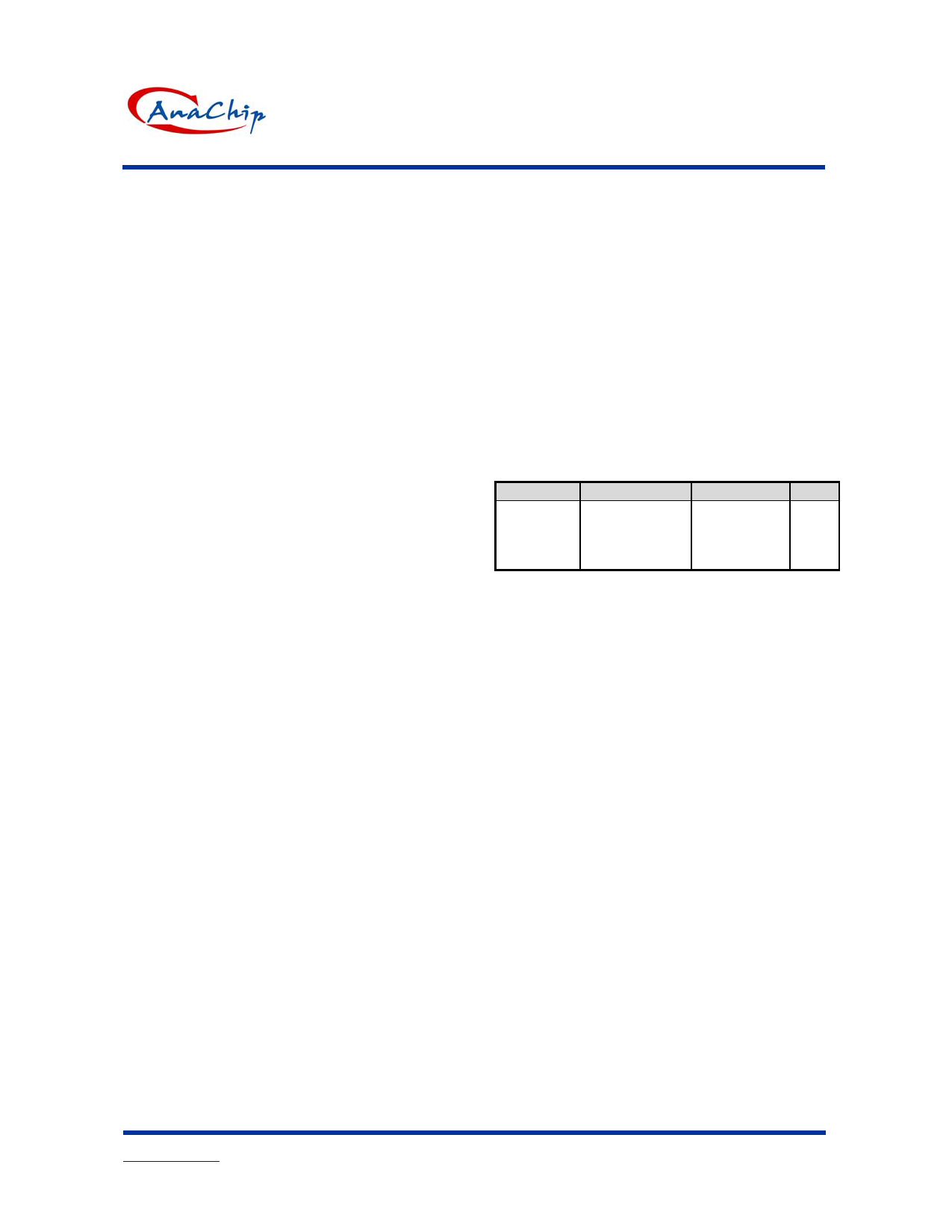

Operation Control Code Chip Select R/W

Read

1010

A2 A1

1

Write

1010

A0

0

A2 A1

A0

Table B

A0, A1, A2 is used to access the AM24LC02.

Write Operations

Byte Write

Following the start signal from the master, the slave

address is placed onto the bus by the master

transmitter. This indicates to the addressed slave

receiver that a byte with a word address will follow

after it has generated an acknowledge bit during the

ninth clock cycle. Therefore the next byte

transmitted by the master is the word address and

will be written into the address pointer of the

AM24LC02. After receiving another acknowledge

signal from the AM24LC02 the master device will

transmit the data word to be written into the

addressed memory location. The AM24LC02

acknowledges again and the master generates a

stop condition. This initiates the internal write cycle,

and during this period the AM24LC02 will not

generate acknowledge signals. (Shown in Figure 4)

Page Write

The write control byte, word address and the first

data byte are transmitted to the AM24LC02 in the

same way as in a byte write. But instead of

generating a stop condition the master transmit up

to 8 data bytes to the AM24LC02 which are

temporarily stored in the on-chip page buffer and will

be written into the memory after the master has

transmitted a stop condition. If the master transmits

more than 8 bytes prior to generating the stop

condition, the address counter will roll over and the

previously received data will be overwritten. As with

the byte write operation, once the stop condition is

received an internal write cycle will begin. (Shown in

Figure 5)

Acknowledge Polling

Since the device will not acknowledge during a write

cycle , this can be used to determine when the cycle

is complete (this feature can be used to maximize

bus throughout). Once the stop condition for a write

command has been issued from the master, the

device initiates the internally timed write cycle. ACK

polling can be initiated immediately. This involves

the master sending a start condition followed by the

control byte for a write command (R/W = 0). If the

device is still busy with the write cycle , then no ACK

will returned. If the cycle is complete then the device

will return the ACK and the master can then proceed

with the next read or write commands.

Anachip Corp.

www.anachip.com.tw

Rev. A1 Oct 20, 2003

6/12