M24C01(2000) гғҮгғјгӮҝгӮ·гғјгғҲгҒ®иЎЁзӨәпјҲPDFпјү - STMicroelectronics

йғЁе“Ғз•ӘеҸ·

гӮігғігғқгғјгғҚгғігғҲиӘ¬жҳҺ

гғЎгғјгӮ«гғј

M24C01 Datasheet PDF : 20 Pages

| |||

M24C16, M24C08, M24C04, M24C02, M24C01

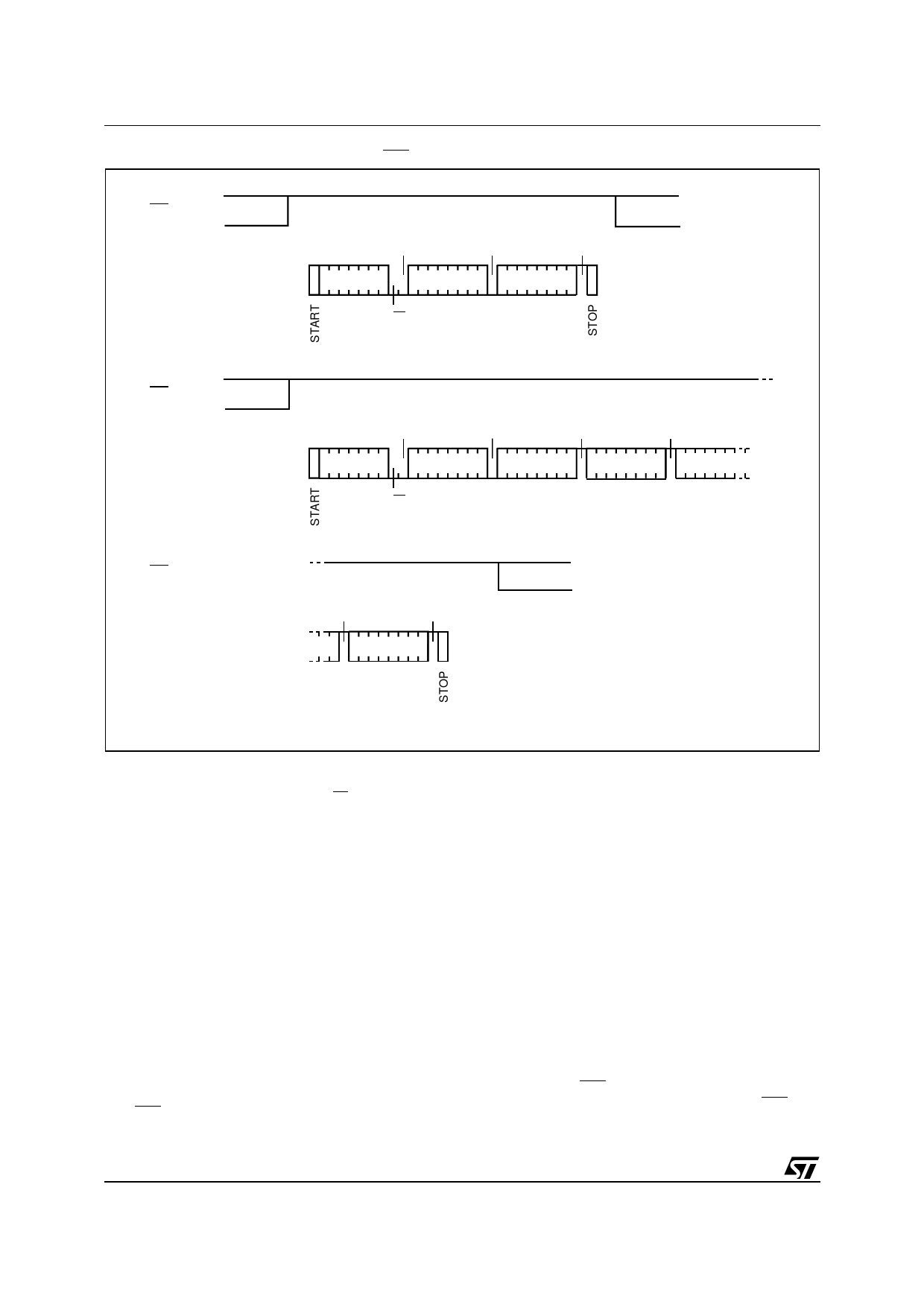

Figure 7. Write Cycle Polling Flowchart using ACK

WRITE Cycle

in Progress

START Condition

DEVICE SELECT

with RW = 0

First byte of instruction

with RW = 0 already

decoded by M24xxx

NO ACK

Returned

YES

Next

NO

Operation is

Addressing the

Memory

ReSTART

YES

Send

Byte Address

STOP

Proceed

WRITE Operation

Proceed

Random Address

READ Operation

AI01847

are all located in the same вҖҷrowвҖҷ in the memory:

that is the most significant memory address bits

are the same. If more bytes are sent than will fit up

to the end of the row, a condition known as вҖҳroll-

overвҖҷ occurs. Data starts to become overwritten, or

otherwise altered.

The master sends from one up to 16 bytes of data,

each of which is acknowledged by the memory if

the WC pin is low. If the WC pin is high, the

contents of the addressed memory location are

not modified, and each data byte is followed by a

NoAck. After each byte is transferred, the internal

byte address counter (the 4 least significant bits

only) is incremented. The transfer is terminated by

the master generating a STOP condition.

When the master generates a STOP condition

immediately after the Ack bit (in the вҖң10th bitвҖқ time

slot), either at the end of a byte write or a page

write, the internal memory write cycle is triggered.

A STOP condition at any other time does not

trigger the internal write cycle.

During the internal write cycle, the SDA input is

disabled internally, and the device does not

respond to any requests.

Minimizing System Delays by Polling On ACK

During the internal write cycle, the memory

disconnects itself from the bus, and copies the

data from its internal latches to the memory cells.

The maximum write time (tw) is shown in Table 6B,

but the typical time is shorter. To make use of this,

an Ack polling sequence can be used by the

master.

8/20