BR24T04FVJ-W データシートの表示(PDF) - ROHM Semiconductor

部品番号

コンポーネント説明

メーカー

BR24T04FVJ-W Datasheet PDF : 37 Pages

| |||

BR24T04-W

Datasheet

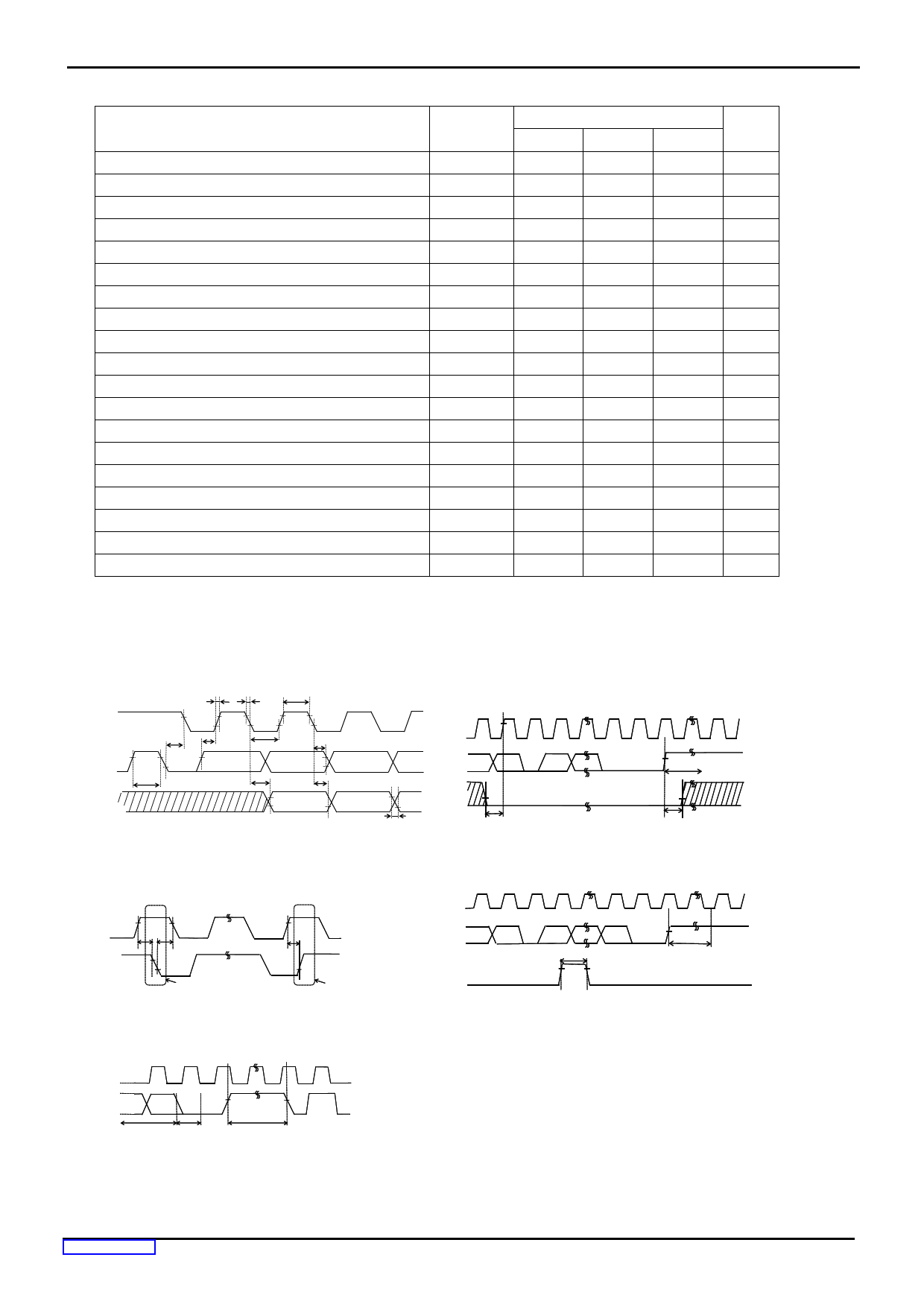

AC Characteristics (Unless otherwise specified, Ta=-40°C to +85°C, Vcc=1.6V to 5.5V)

Parameter

Limit

Symbol

Unit

Min

Typ

Max

Clock Frequency

fSCL

-

-

400

kHz

Data Clock High Period

tHIGH

0.6

-

-

µs

Data Clock Low Period

tLOW

1.2

-

-

µs

SDA,SCL(INPUT) Rise Time (1)

tR

-

-

1.0

µs

SDA,SCL (INPUT)Fall Time (1)

tF1

-

-

1.0

µs

SDA(OUTPUT)Fall Time (1)

tF2

-

-

0.3

µs

Start Condition Hold Time

tHD:STA

0.6

-

-

µs

Start Condition Setup Time

tSU:STA

0.6

-

-

µs

Input Data Hold Time

tHD:DAT

0

-

-

ns

Input Data Setup Time

tSU:DAT

100

-

-

ns

Output Data Delay Time

tPD

0.1

-

0.9

µs

Output Data Hold Time

tDH

0.1

-

-

µs

Stop Condition Setup Time

tSU:STO

0.6

-

-

µs

Bus Free Time

tBUF

1.2

-

-

µs

Write Cycle Time

tWR

-

-

5

ms

Noise Spike Width (SDA and SCL)

tI

-

-

0.1

µs

WP Hold Time

tHD:WP

1.0

-

-

µs

WP Setup Time

tSU:WP

0.1

-

-

µs

WP High Period

tHIGH:WP

1.0

-

(1) Not 100% TESTED.

Condition Input Data Level:VIL=0.2×Vcc VIH=0.8×Vcc

Input Data Timing Reference Level: 0.3×Vcc/0.7×Vcc

Output Data Timing Reference Level: 0.3×Vcc/0.7×Vcc

Rise/Fall Time : ≤20ns

-

µs

Serial Input / Output Timing

tR

tF1

tHIGH

SCL

70%

SDA

((I入NP力U) T)

tHD:STA

70%

30%

tBUF

70%

70% 70%

30%

30%

tSU:DAT

tLOW

70%

tPD

70%

30%

70%

30%

tHD:DAT

70%

30%

tDH

SDA

((O出U力T)PUT)

70%

30%

30%

○Input read at the rise edge of SCL

S(oDuAtput)○Data

output

in

sync

with

the

70%

fall30o% f

SCL

70%

30%

70%

30%

tF2

Figure 2-(a). Serial Input / Output Timing

70%

DATA(1)

D1

D0 ACK

DATA(n)

ACK

70%

tWR

30%

30%

ttSSUU::WWPP

tHD:WPP

SSTTOOPP CCOONNDDIITTIIOONN

Figure 2-(d). WP Timing at Write Execution

70%

70%

70%

tSU:STA

tHD:STA

70%

30%

START CONDITION

tSU:STO

30%

STOP CONDITION

30%

30%

FiguSrTeART2C-ON(DbIT)IO.N Start-Stop Bit Timing STOP CONDITION

DDAATTAA((11))

DDAATTAA((nn))

DD11

DD00 AACCKK

ttHHIIGGHH::WWPP

Fig1-(4) Write7700c%%ycle tim77i00n%%g

AACCKK

7700%%

ttWWRR

Fig1-(5) WP timing at write execution

FFigi1g-u(6re) 2W-P(et)im. iWngPatTwimritiencganacteWl rite Cancel

D0

write data

(n-th address)

ACK

70%

70%

tWR

STOP CONDITION START CONDITION

Figure 2-(c). Write Cycle Timing

www.rohm.com

©2013 ROHM Co., Ltd. All rights reserved.

TSZ22111 • 15 • 001

Fig1-(5) WP timing at write execution

Fig1-(6) WP timing at write cancel

3/33

TSZ02201-0R2R0G100080-1-2

11.Jun.2019 Rev.005