MC68HC000FN8 データシートの表示(PDF) - Motorola => Freescale

部品番号

コンポーネント説明

メーカー

MC68HC000FN8 Datasheet PDF : 26 Pages

| |||

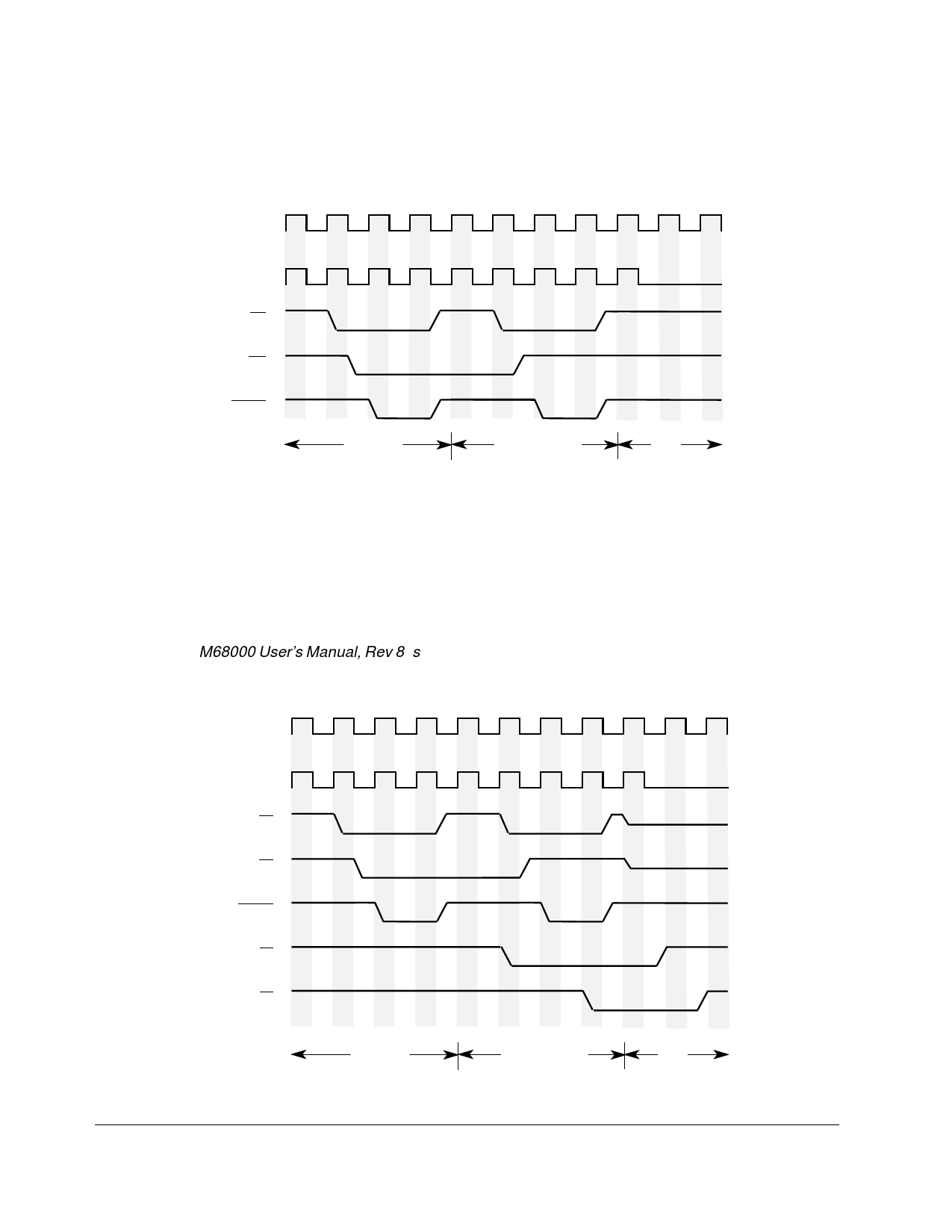

8-bit mode requires two bus cycles to fetch the immediate data of the STOP instruction. After the

processor clock is disabled, it is often necessary to disable the clock to other sections of your circuit.

This can be done, but be careful that runt clocks and spurious glitches are not presented to the

MC68SEC000. A timing diagram is shown in Figure 4.

CLK

S0 S1 S2 S3 S4 S5 S6 S7 S0 S1 S2 S3 S4 S5 S6 S7

CPU_CLK

AS

RW

DTACK

Write to

Low-Power

Address

Fetch Immediate

Data of STOP

Stop

Instruction

Figure 4. MC68SEC000 Clock Stop Timing for 16-Bit Data Bus

Note: While the MC68SEC000 is in the low-power mode, all inputs must be driven to VDD or VSS, or have a

pull-up or pull-down resistor.

3. This step is optional depending on whether your applications require the MC68SEC000 signals with

three-state capability to be placed into a high-impedance state. To place the MC68SEC000 into a

three-state condition, the proper method for arbitrating the bus (as described in 5.2 Bus Arbitration

in the M68000 User’s Manual, Rev 8) should be completed during the fetch of the status register data

for the STOP instruction. A timing diagram with the bus arbitration sequence is shown in Figure 5.

CLK

S0 S1 S2 S3 S4 S5 S6 S7 S0 S1 S2 S3 S4 S5 S6 S7

CPU_CLK

AS

RW

DTACK

BR

BG

Write to

Fetch Immediate

Low-Power

Data of STOP

Stop

Address

Instruction

Figure 5. MC68SEC000 Clock Stop Timing with Bus Arbitration for 16-Bit Data Bus

6

M68000 USER’S MANUAL ADDENDUM

MOTOROLA