AK4541 データシートの表示(PDF) - Asahi Kasei Microdevices

部品番号

コンポーネント説明

メーカー

AK4541 Datasheet PDF : 31 Pages

| |||

[ASAHI KASEI]

[AK4541]

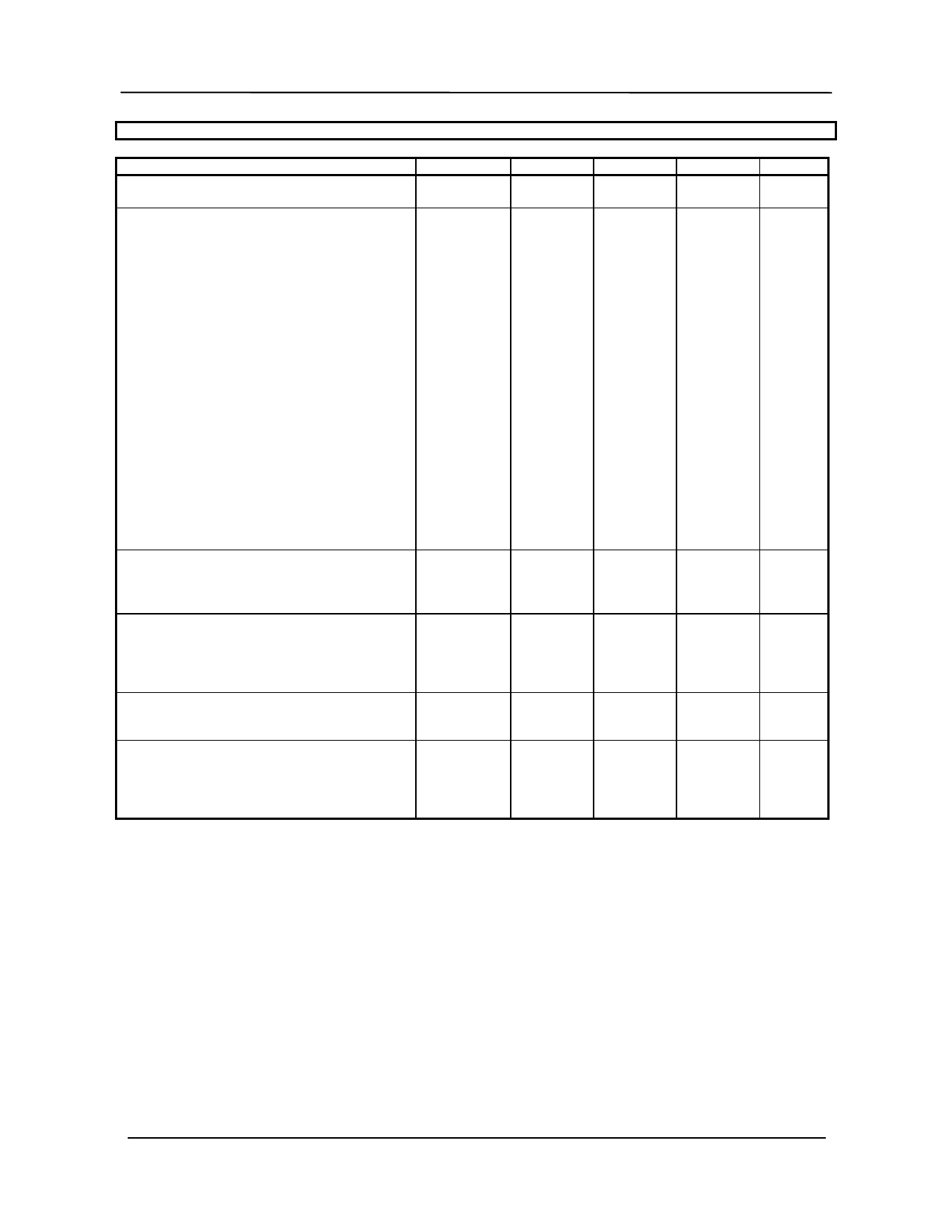

Switching Characteristics

Ta=25°C, AVdd=DVdd=3.3V±5%, 50pF external load

Parameter

Symbol

min

Typ

max

Units

Master Clock Frequency Note)

If Crystal is not used.

Fmclk

-

24.576

-

MHz

45

50

55

%

AC link Interface Timing

BIT_CLK frequency

Fbclk

12.288

MHz

BIT_CLK clock Period(Tbclk=1/Fbclk)

Tbclk

-

81.38

ns

BIT_BLK low pulse width

Tclk_low

36.0

40.7

45

ns

BIT_BLK low pulse width

Tclk_high

36.0

40.7

45

ns

BIT_CLK rise time

Trise_clk

-

-

6

ns

BIT_CLK fall time

SYNC frequency

SYNC low pulse width

SYNC high pulse width

SYNC rise time

SYNC fall time

Setup time(SDATA_IN,SDATA_OUT)

Hold time(SDATA_IN,SDATA_OUT)

SDATA_IN delay time from BIT_CLK

rising edge

Tfall_clk

Tsync_low

Tsync_high

Trise_sync

Tfall_sync

Tsetup

Thold

Tdelay

-

-

6

-

48

-

-

19.5

-

(240 cycle)

-

1.3

-

(16 cycle)

-

-

6

-

-

6

10.0

-

-

25.0

-

-

-

15

ns

kHz

µs

(Tbclk)

µs

(Tbclk)

ns

ns

ns

ns

ns

SDATA_IN rise time

SDATA_IN fall time

SDATA_OUT rise time

SDATA_OUT fall time

Trise_din

-

-

6

ns

Tfall_din

-

-

6

ns

Trise_dout

-

-

6

ns

Tfall_dout

-

-

6

ns

Cold Rest (SDATA_OUT=L, SYNC=L)

RESET# active low pulse width

Trst_low

1.0

-

RESET# inactive to BIT_CLK delay

Trst2clk

162.8

(2 cycle)

-

µs

ns

(Tbclk)

Warm Rest Timing

SYNC active low pulse width

SYNC inactive to BIT_CLK delay

Tsync_high

1.0

1.3

-

µs

(16 cycle)

(Tbclk)

Tsync2clk

162.8

ns

(2 cycle)

(Tbclk)

AC-link Low Power Mode Timing

End of Slot 2 to BIT_CLK, SDATA_IN

Ts2_pdwn

-

Low

-

1.0

µs

Activate Test Mode Timing

Setup to trailing edge of RESET#

Hold from RESET# rising edge

Rising edge of RESET# to Hi-Z

Falling edge of RESET# to L

Tsetup2rst

15.0

-

Thold2rst

100

-

Toff

-

-

Tlow

-

-

-

ns

-

ns

50

ns

50

ns

Note ) The use of a crystal is recommended. If a master clock is supplied (or if an external oscillator is used),

Master Clock should be supplied to XTAL_IN and XTAL_OUT should be left open.

<M0047-E-01>

-7-

1999/01