AD9841A データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9841A Datasheet PDF : 23 Pages

| |||

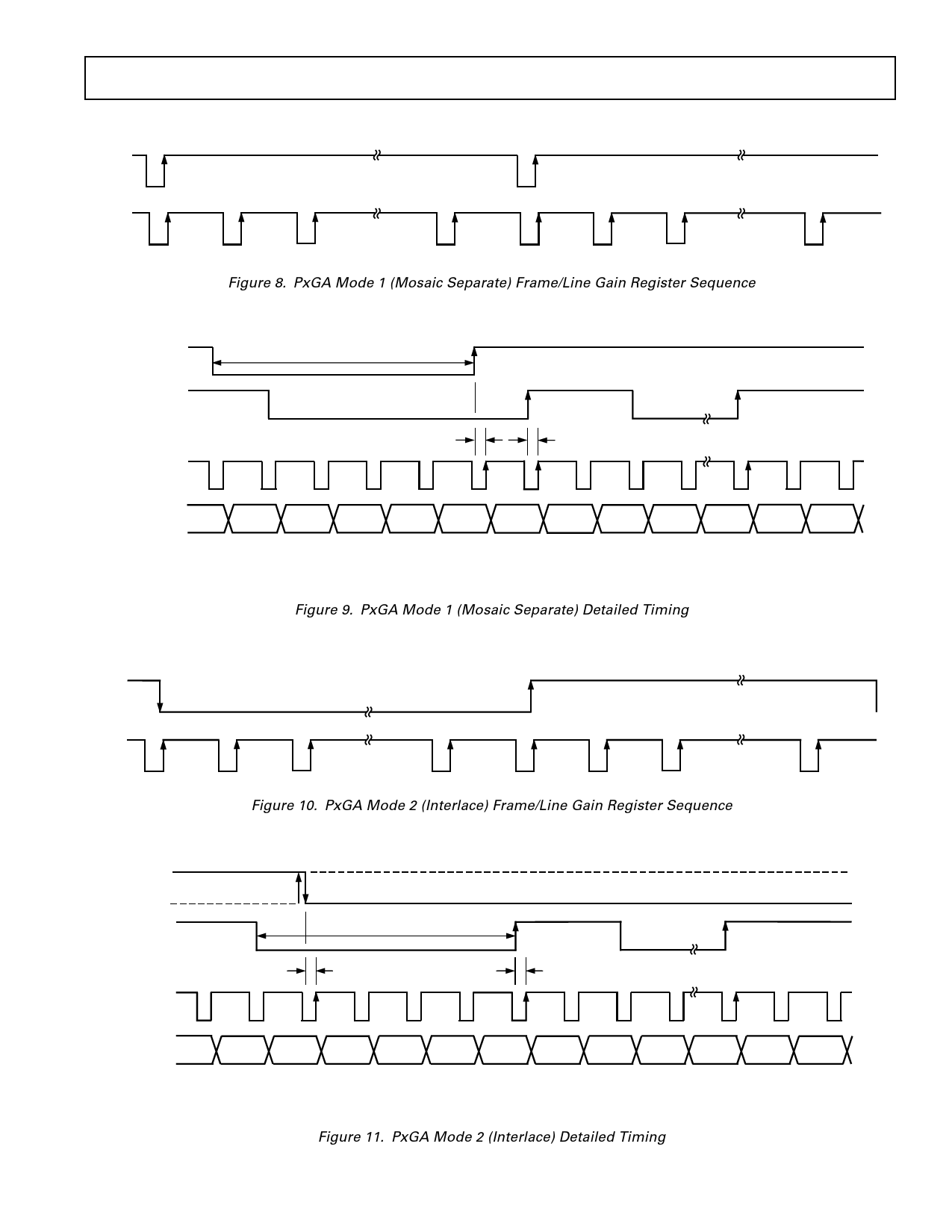

PIXEL GAIN AMPLIFIER (PxGA) TIMING

AD9841A/AD9842A

VD

FRAME n

FRAME n+1

0101...

2323...

0101...

0101...

2323...

0101...

HD

LINE 0

LINE 1

LINE 2

LINE m–1

LINE m

LINE 0

LINE 1

LINE 2

LINE m–1

NOTE: 0 = GAIN0, 1 = GAIN1, 2 = GAIN2, 3 = GAIN3

Figure 8. PxGA Mode 1 (Mosaic Separate) Frame/Line Gain Register Sequence

LINE m

5 PIXEL MIN

VD

HD

3ns MIN

3ns MIN

SHP

PxGA GAIN

GAINX

GAIN0

GAIN1 GAIN0

GAINX

NOTES:

1. MINIMUM PULSEWIDTH FOR HD AND VD IS 5 PIXEL CYCLES.

2. BOTH VD AND HD ARE INTERNALLY UPDATED AT SHP RISING EDGES. MINIMUM SET-UP TIME IS 3ns.

3. EVERY HD RISING EDGE WITH A PREVIOUS VD RISING EDGE WILL RESET TO 0101.

4. EVERY HD RISING EDGE WITHOUT A PREVIOUS VD RISING EDGE WILL ALTERNATE BETWEEN 0101... AND 2323.

Figure 9. PxGA Mode 1 (Mosaic Separate) Detailed Timing

GAIN2

GAIN3

VD

EVEN FIELD

ODD FIELD

0101...

2323...

0101...

0101...

2323...

0101...

HD

LINE 0

LINE 1

LINE 2

LINE m–1

LINE m

LINE 0

LINE 1

LINE 2

LINE m–1

NOTE: 0 = GAIN0, 1 = GAIN1, 2 = GAIN2, 3 = GAIN3

Figure 10. PxGA Mode 2 (Interlace) Frame/Line Gain Register Sequence

LINE m

VD

HD

SHP

3ns MIN

5 PIXEL MIN

3ns MIN

PxGA

GAIN

GAINX

GAIN0

GAIN1

GAIN0

GAINX

NOTES:

1. BOTH VD AND HD ARE INTERNALLY UPDATED AT SHP RISING EDGES.

2. EVERY HD RISING EDGE WITH A PREVIOUS VD RISING OR FALLING EDGE WILL RESET TO 0101.

3. EVERY HD RISING EDGE WITHOUT A PREVIOUS VD RISING EDGE WILL ALTERNATE BETWEEN 0101... AND 2323.

Figure 11. PxGA Mode 2 (Interlace) Detailed Timing

GAIN2

GAIN3

REV. 0

–11–