HMS30C7202N データシートの表示(PDF) - MagnaChip Semiconductor

部品番号

コンポーネント説明

メーカー

HMS30C7202N Datasheet PDF : 179 Pages

| |||

18:17

16

15

14

13

12

11:6

5:0

5.4 Timings

5.4.1 Reset Sequences of Power On Reset

HMS30C7202N

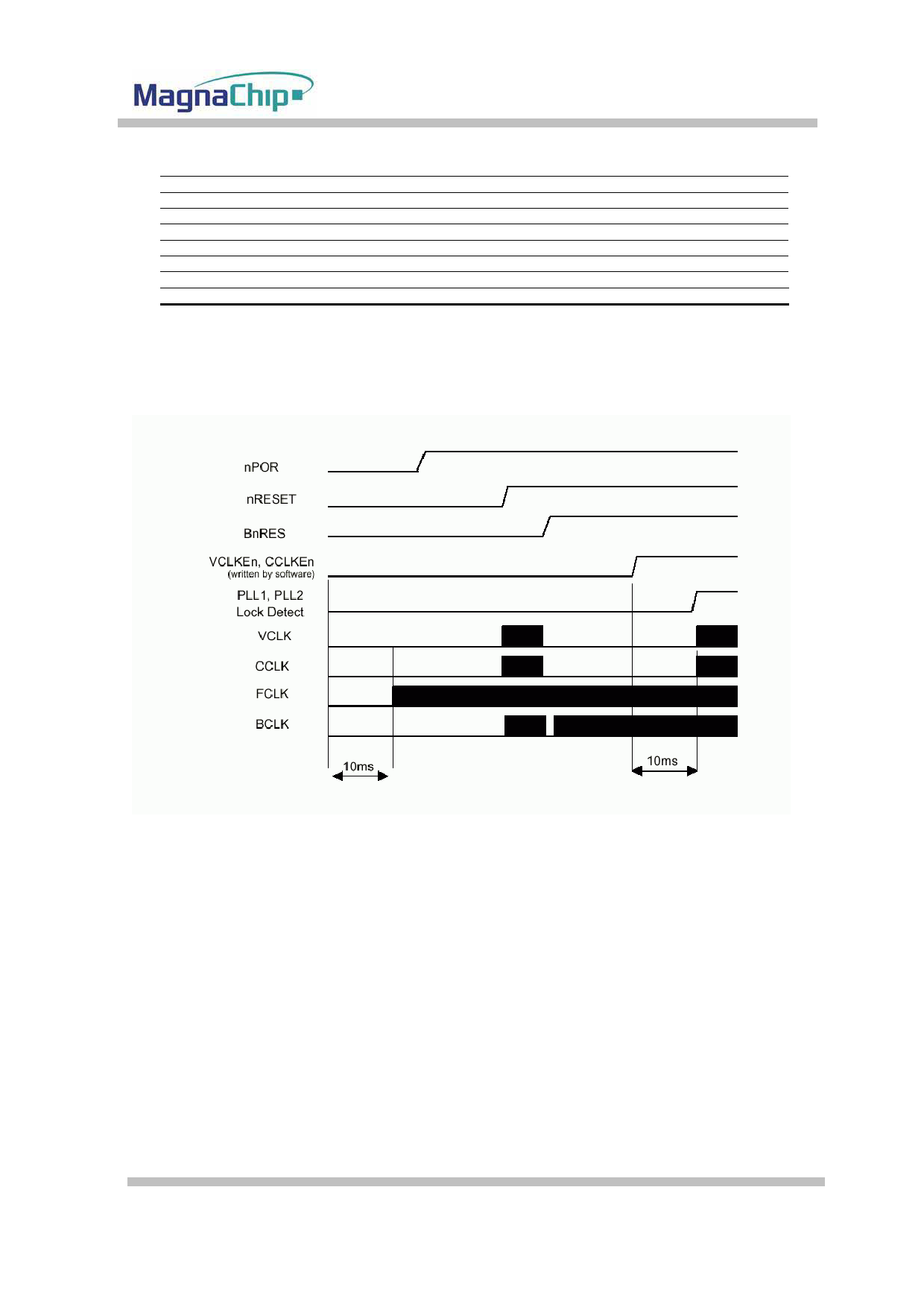

Figure 5-2 PMU Cold Reset Event

In the event of removal and re-application of all power to the HMS30C7202, the following sequence may be

typical:

z nPOR input is active. All internal registers are reset to their default values. The PMU drives nRESETout LOW to reset any

off-chip peripheral devices.

z BnRES becomes active on exit from the nPOR condition. Clocks are enabled temporarily to allow synchronous resets to

operate.

z The default frequency of FCLK on exit from nPOR will be 70.0416 MHz.

z When FCLK is stable, the CPU clock is released. If the CPU were to read the RESET/Status register at this time, it will

return 0x10f as a initial value.

z If you are to clear these flag bits, write 0x10f to the RESET register. (Refer 5.3.4 PMU Reset/PLL Status Register).

z The CPU writes 0x20 to the clock control register, which will set a FCLK speed of 58.9824MHz. The new clock frequency,

however, is not adopted until the

z PMU has entered and left DEEP SLEEP mode.

z The CPU sets a RTC timer alarm to expire in approximately 2 seconds

z The CPU sets DEEP SLEEP into the PMU Mode Register

z The PMU state machine will enter DEEP SLEEP mode (via the intermediate states shown in Figure 5-1: Power

Management State Diagram).

z When the RTC timer alarm is activated, the PMU automatically wakes up into SLOW mode, but with the new FCLK

© 2004 MagnaChip Semiconductor Ltd. All Ri3g4hts Reserved.

- 34 -

Version 1.1