49LF002 データシートの表示(PDF) - Silicon Storage Technology

部品番号

コンポーネント説明

メーカー

49LF002 Datasheet PDF : 36 Pages

| |||

2 Mbit / 3 Mbit / 4 Mbit / 8 Mbit Firmware Hub

SST49LF002A / SST49LF003A / SST49LF004A / SST49LF008A

Advance Information

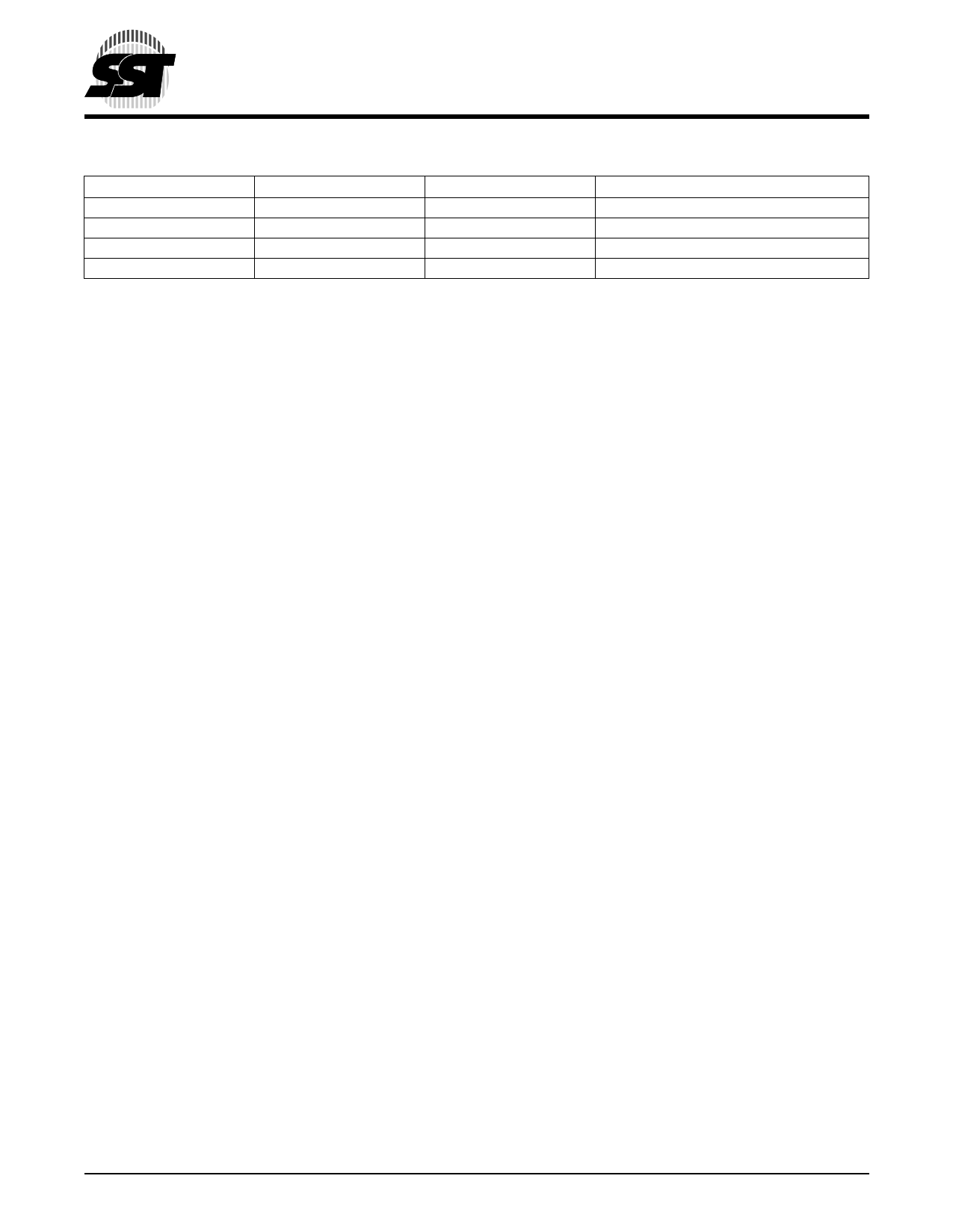

TABLE 6: BLOCK LOCKING REGISTER BITS

Reserved Bit [7..2]

000000

000000

000000

000000

Lock-Down Bit [1]

0

0

1

1

Write-Lock Bit [0]

0

1

0

1

Lock Status

Full Access

Write Locked (Default State at Power-Up)

Locked Open (Full Access Locked Down)

Write Locked Down

T6.3 504

Write Lock

The Write-Lock bit, bit 0, controls the lock state described in

Table 6. The default Write status of all blocks after power-

up is write locked. When bit 0 of the Block Locking register

is set, Program and Erase operations for the corresponding

block are prevented. Clearing the Write-Lock bit will unpro-

tect the block. The Write-Lock bit must be cleared prior to

starting a Program or Erase operation since it is sampled at

the beginning of the operation.

The Write-Lock bit functions in conjunction with the hard-

ware Write Lock pin TBL# for the top Boot Block. When

TBL# is low, it overrides the software locking scheme. The

top Boot Block Locking register does not indicate the state

of the TBL# pin.

The Write-Lock bit functions in conjunction with the hard-

ware WP# pin for blocks 0 to 6. When WP# is low, it over-

rides the software locking scheme. The Block Locking

register does not indicate the state of the WP# pin.

Lock Down

The Lock-Down bit, bit 1, controls the Block Locking regis-

ter as described in Table 6. When in the FWH interface

mode, the default Lock Down status of all blocks upon

power-up is not locked down. Once the Lock-Down bit is

set, any future attempted changes to that Block Locking

register will be ignored. The Lock-Down bit is only cleared

upon a device reset with RST# or INIT# or power down.

Current Lock Down status of a particular block can be

determined by reading the corresponding Lock-Down bit.

Once a block’s Lock-Down bit is set, the Write-Lock bits for

that block can no longer be modified, and the block is

locked down in its current state of write accessibility.

JEDEC ID Registers

The JEDEC ID registers for the boot device appear at

FFBC0000H and FFBC0001H in the 4 GByte system

memory map, and will appear elsewhere if the device is not

the boot device. Register is not available for read when the

device is in Erase/Program operation. Unused register

location will read as 00H. Refer to the relevant application

note for details. See Table 7 for the device ID code.

PARALLEL PROGRAMMING MODE

Device Operation

Commands are used to initiate the memory operation func-

tions of the device. The data portion of the software com-

mand sequence is latched on the rising edge of WE#.

During the software command sequence the row address

is latched on the falling edge of R/C# and the column

address is latched on the rising edge of R/C#.

Read

The Read operation of the SST49LF00xA device is con-

trolled by OE#. OE# is the output control and is used to

gate data from the output pins. Refer to the Read cycle

timing diagram, Figure 14, for further details.

Reset

A VIL on RST# pin initiates a device reset.

Byte-Program Operation

The SST49LF00xA device is programmed on a byte-by-

byte basis. Before programming, one must ensure that the

sector, in which the byte which is being programmed exists,

is fully erased. The Byte-Program operation is initiated by

executing a four-byte command load sequence for Soft-

ware Data Protection with address (BA) and data in the last

byte sequence. During the Byte-Program operation, the

row address (A10-A0) is latched on the falling edge of R/C#

and the column Address (A21-A11) is latched on the rising

edge of R/C#. The data bus is latched in the rising edge of

WE#. The Program operation, once initiated, will be com-

pleted, within 20 µs. See Figure 15 for Program operation

timing diagram, Figure 18 for timing waveforms, and Figure

26 for its flowchart. During the Program operation, the only

valid reads are Data# Polling and Toggle Bit. During the

internal Program operation, the host is free to perform addi-

tional tasks. Any commands written during the internal Pro-

gram operation will be ignored.

©2001 Silicon Storage Technology, Inc.

8

S71161-06-000 9/01 504