AD9627ABCPZ-150 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9627ABCPZ-150

AD9627ABCPZ-150 Datasheet PDF : 76 Pages

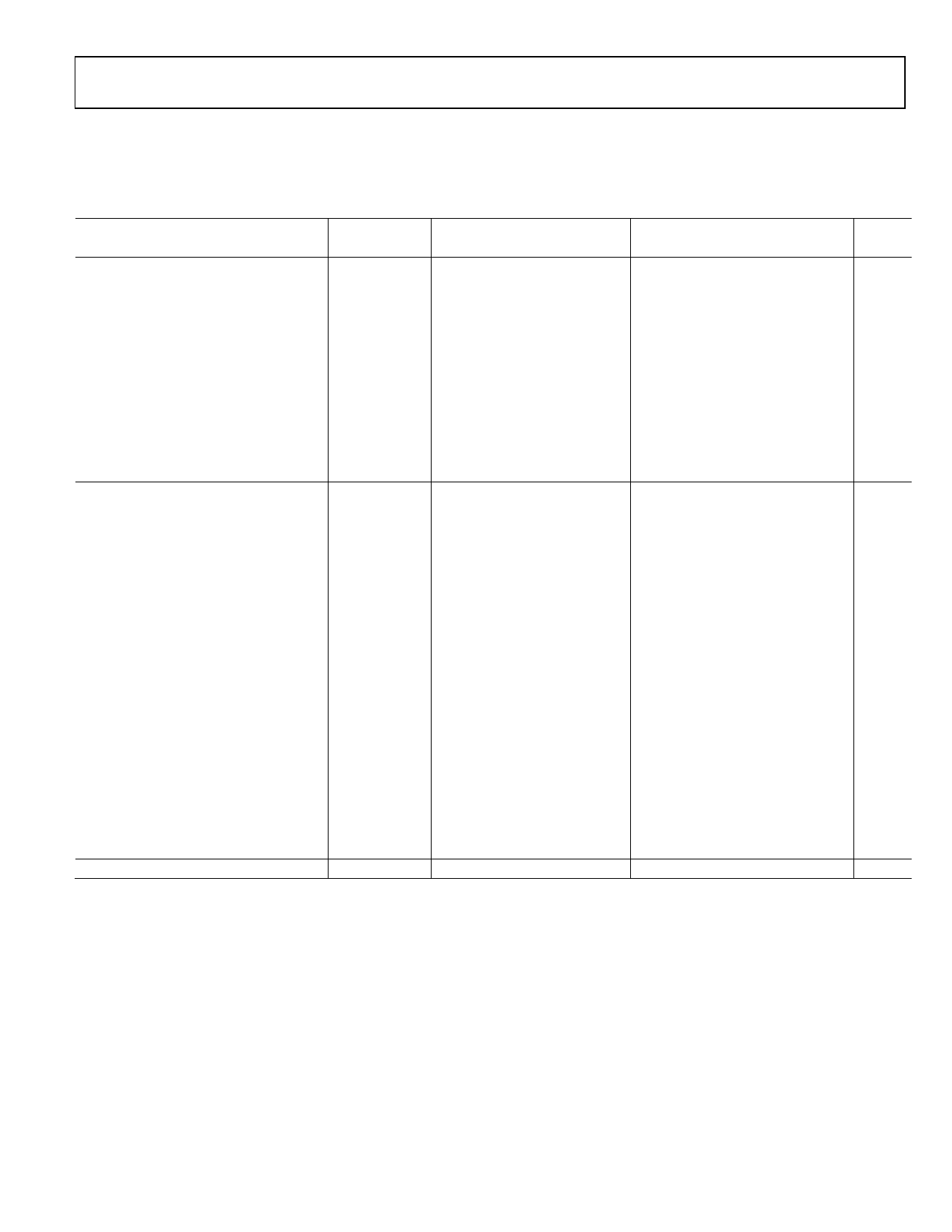

| |||

AD9627

SWITCHING SPECIFICATIONS—AD9627-80/AD9627-105

AVDD = 1.8 V, DVDD = 1.8 V, DRVDD = 3.3 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, and

DCS enabled, unless otherwise noted.

Table 6.

AD9627-80

AD9627-105

Parameter

Temperature Min

Typ

Max

Min

Typ

Max

CLOCK INPUT PARAMETERS

Input Clock Rate

Full

625

625

Conversion Rate

DCS Enabled1

Full

20

80

20

105

DCS Disabled1

Full

10

80

10

105

CLK Period—Divide-by-1 Mode (tCLK) Full

12.5

9.5

CLK Pulse Width High

Divide-by-1 Mode, DCS Enabled

Full

3.75

6.25

8.75

2.85

4.75

6.65

Divide by-1-Mode, DCS Disabled Full

5.63

6.25

6.88

4.28

4.75

5.23

Divide-by-2 Mode, DCS Enabled

Full

1.6

1.6

Divide-by-3 Through Divide-by-8

Full

0.8

0.8

Modes, DCS Enabled

DATA OUTPUT PARAMETERS (DATA, FD)

CMOS Mode—DRVDD = 3.3 V

Data Propagation Delay (tPD)2

Full

2.2

4.5

6.4

2.2

4.5

6.4

DCO Propagation Delay (tDCO)

Full

3.8

5.0

6.8

3.8

5.0

6.8

Setup Time (tS)

Full

6.25

5.25

Hold Time (tH)

Full

5.75

4.25

CMOS Mode—DRVDD = 1.8 V

Data Propagation Delay (tPD)2

Full

2.4

5.2

6.9

2.4

5.2

6.9

DCO Propagation Delay (tDCO)

Full

4.0

5.6

7.3

4.0

5.6

7.3

Setup Time (tS)

Full

6.65

5.15

Hold Time (tH)

Full

5.85

4.35

LVDS Mode—DRVDD = 1.8 V

Data Propagation Delay (tPD)2

Full

2.0

4.8

6.3

2.0

4.8

6.3

DCO Propagation Delay (tDCO)

Full

5.2

7.3

9.0

5.2

7.3

9.0

CMOS Mode Pipeline Delay (Latency) Full

12

12

LVDS Mode Pipeline Delay (Latency) Full

Channel A/Channel B

12/12.5

12/12.5

Aperture Delay (tA)

Full

1.0

1.0

Aperture Uncertainty (Jitter, tJ)

Full

0.1

0.1

Wake-Up Time3

Full

350

350

OUT-OF-RANGE RECOVERY TIME

Full

2

2

Unit

MHz

MSPS

MSPS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Cycles

Cycles

ns

ps rms

μs

Cycles

1 Conversion rate is the clock rate after the divider.

2 Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with 5 pF load.

3 Wake-up time is dependent on the value of the decoupling capacitors.

Rev. B | Page 11 of 76