AD9929 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9929 Datasheet PDF : 64 Pages

| |||

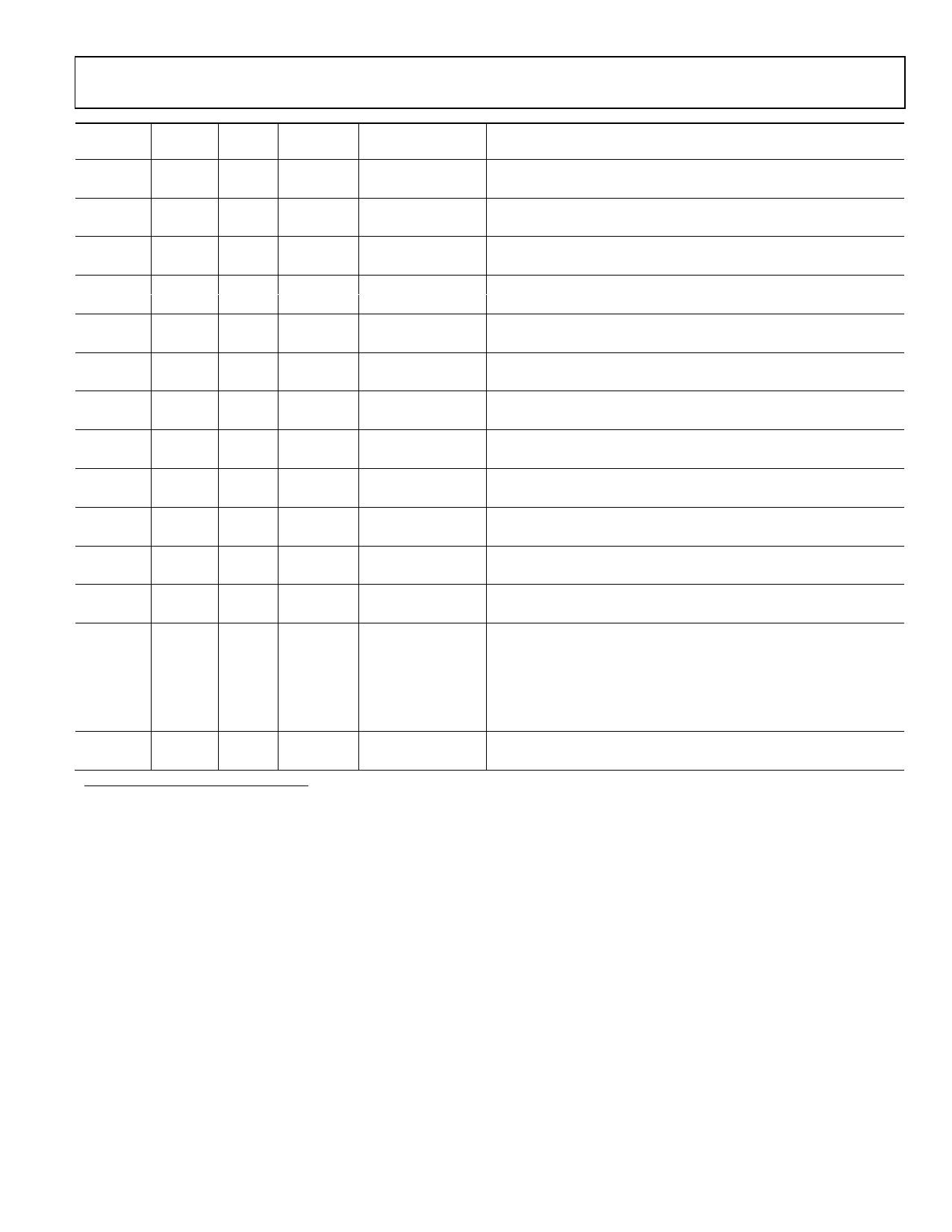

AD9929

Address

0x1B

0x1C

0x1D

0x1E

0x1F

0x20

0x21

0x22

0x23

0x24

0x25

0x26

0xD5

Content

(23:13)

(12:0)

(23:13))

(12:0

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:13)

(12:0)

(23:4)

Bit

Width

11

13

11

13

11

13

11

13

11

13

11

13

11

13

11

13

11

13

11

13

11

13

11

13

20

3

1

Default

Value

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

–

0x1FFF

0x00000

1

Register Name

Unused

XV3SPAT_TOG1

Unused

XV3SPAT_TOG2

Unused

XV4SPAT_TOG1

Unused

XV4SPAT_TOG2

Unused

XV1SPAT_TOG1

Unused

XV1SPAT_TOG2

Unused

XV2SPAT_TOG1

Unused

XV2SPAT_TOG2

Unused

XV3SPAT_TOG1

Unused

XV3SPAT_TOG2

Unused

XV4SPAT_TOG1

Unused

XV4SPAT_TOG2

Unused

DCLK2SEL

0xD6

2

1

(1:0)

2

(23:1) 23

0

1

0

0

0x000000

1

DCLK1SEL

CLKDIV

Unused

SLAVE_MODE

Register Description

XV3SPAT Toggle Position #1 (Mode_A active)

XV3SPAT Toggle Position #2 (Mode_A active)

XV4SPAT Toggle Position #1 (Mode_A active)

XV4SPAT Toggle Position #2 (Mode_A Active)

XV1SPAT Toggle Position #1 (Mode_A Active)

XV1SPAT Toggle Position #2 (Mode_B Active)

XV2SPAT Toggle Position #1 (Mode_B Active)

XV2SPAT Toggle Position #2 (Mode_B Active)

XV3SPAT Toggle Position #1 (Mode_B Active)

XV3SPAT Toggle Position #2 (Mode_B Active)

XV4SPAT Toggle Position #1 (Mode_B Active)

XV4SPAT Toggle Position #2 (Mode_B Active)

DCLK2 Selector (0 = Select Internal FD Signal To Be Output on

FD/DCLK2 Pin 16, 1 = Select CLI To Be Output on FD/DCLK2 Pin 16)

DCLK1 Selector (0 = Select DLL Version for DCLK1 Output, 1 = Select

CLI for DCLK1 Output)

Input Clock Divider (0 = No Division, 1 = 1/2, 2 = 1/3, 3 = 1/4)

Operating Mode ( 0 = Master Mode, 1 = Slave Mode)

1 This register defaults to VD synchronous mode type at power-up. VD sync type registers do not get updated until the first falling edge of VD is asserted after the

register has been programmed. VD sync type registers can be programmed to be asynchronous registers by setting VDMODE = 1 (Address 0x01).

Rev. A | Page 13 of 64