AD9929 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9929 Datasheet PDF : 64 Pages

| |||

AD9929

THEORY OF OPERATION

MODES OF OPERATION

Slave and Master Mode Operation

The AD9929 can be operated in either slave or master mode.

It defaults to slave mode operation at power-up. The

SLAVE_MODE register (Address 0xD6) can be used to

configure the AD9929 into master mode by setting

SLAVE_MODE = 0.

Slave Mode Operation

While operating in slave mode, VD, HD, and VGATE are pro-

vided externally from the image processor. VGATE is input

active high on Pin 45.

Unlike master mode operation, there is a 7 CLI clock cycle delay

from the falling edge of HD to when the 12-bit gray code H

counter is reset to 0 (See Figure 62).

Master Mode Operation

While operating in master mode, VD and HD are outputs

and the SYNC/VGATE pin is configured for an external

SYNC input. Master mode is selected by setting register

SLAVE_MODE (Address 0x06) = 0.

HORIZONTAL AND VERTICAL COUNTERS

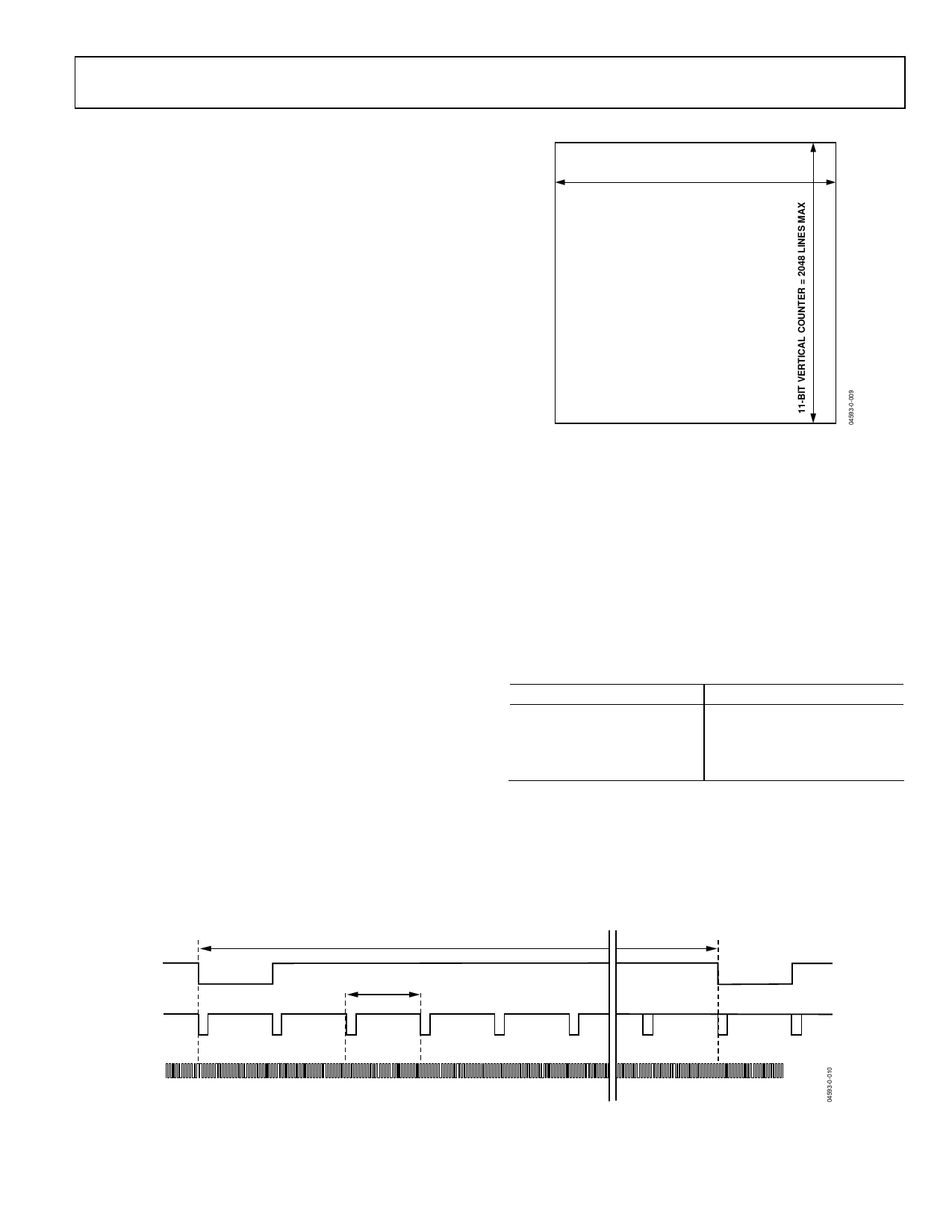

Figure 8 and Figure 9 show the horizontal and vertical counter

dimensions for the AD9929. All internal horizontal and vertical

clocking is programmed using these dimensions to specify line

and pixel locations.

CLI INPUT CLOCK DIVIDER

The AD9929 provides the capability of dividing the CLI input

clock using Register CLKDIV (Address 0xD5). The following

procedure must be followed to reset the AFE and digital circuits

when CLKDIV is reprogrammed back to 0 from CLKDIV = 1,

2, or 3. The DCLK1 output becomes unstable if this procedure

isn’t followed.

Step 1: CLKDIV = 1, 2, or 3 (CLI divided by setting value)

Step 2: CLKDIV = 0 (CLI reprogrammed for no division)

Step 3: DIGSTBY = AFESTBY = 0

Step 4: DIGSTBY = AFESTBY = 1

MAXIMUM FIELD DIMENSIONS

12-BIT HORIZONTAL COUNTER = 4096 PIXELS MAX

Figure 8. Horizontal and Vertical Counters

GRAY CODE REGISTERS

See Table 12 for a list of the AD9929 registers requiring gray

code values. The following is an example of applying a gray

code number for HDLEN using a line length of 1560 pixels:

HDLEN = (1560–4) = 155610 (see Special Note about the

HDLEN Register section).

Where 155610 = Address 0x51E

The gray code value of Address 0x51E would be programmed in

the 12-bit HDLEN register.

Table 12. AD9929 Gray Code Registers

Register Name

Register Type

HDLEN

System_Reg(12)

CLPOBTOG1

System_Reg(15)

CLPOBTOG2

System_Reg(16)

HDLASTLEN

Mode_Reg(1)

MAX VD LENGTH IS 2048 LINES

VD

MAX HD LENGTH IS 4095 PIXELS

HD

CLI

Figure 9. Maximum VD/HD Dimensions

Rev. A | Page 19 of 64