CS4922 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS4922 Datasheet PDF : 33 Pages

| |||

CS4922

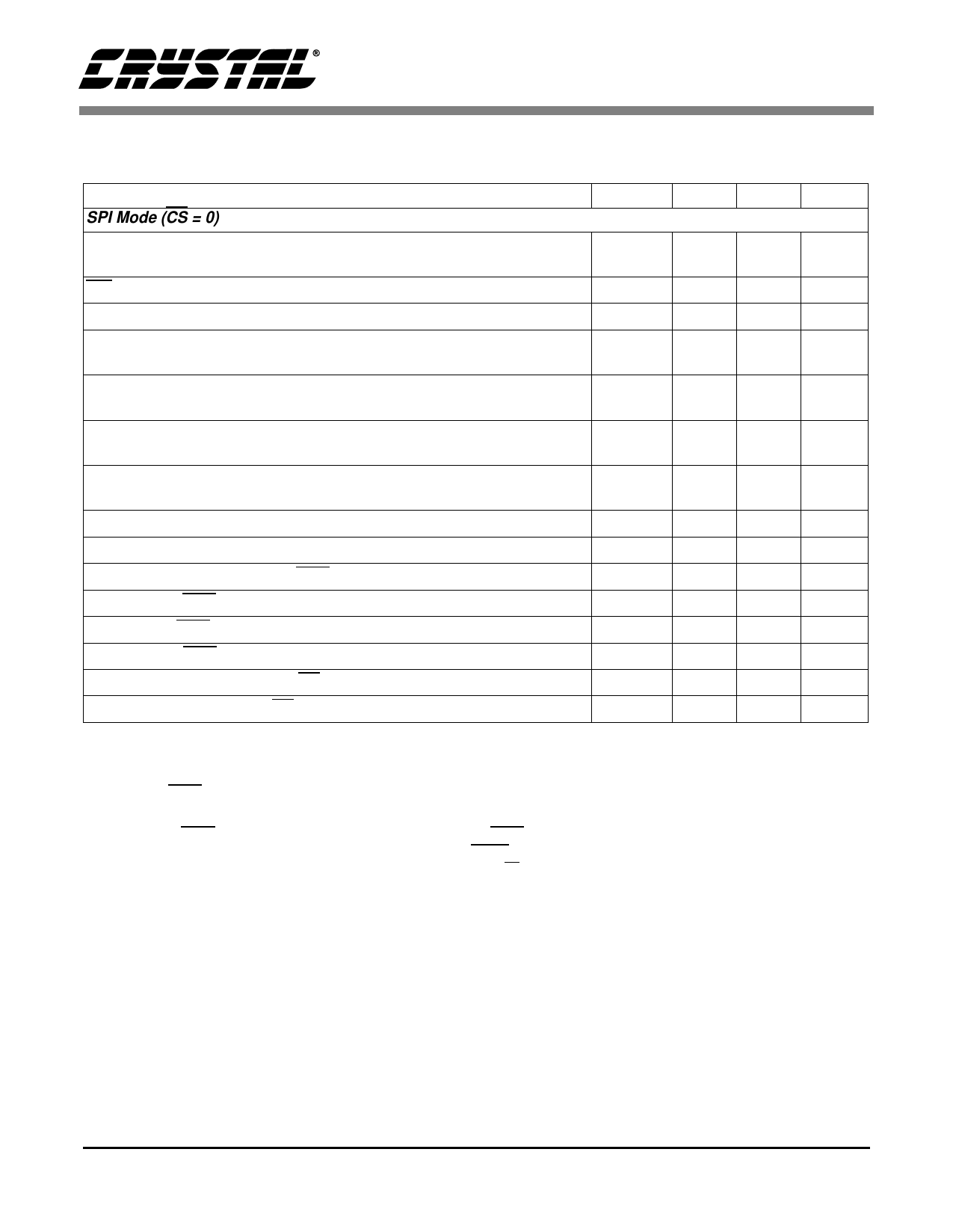

SWITCHING CHARACTERISTICS - CONTROL PORT (SPI MODE) (TA = 25 °C;

VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, CL = 20pF)

SPI Mode (CS = 0)

Parameter

Symbol Min Max Units

SCK/SCL Clock Frequency

CS Falling to SCK/SCL Rising (slow mode)

Rise Time of Both CDIN and SCK/SCL Lines

Fall Time of Both CDIN and SCK/SCL Lines

SCK/SCL Low Time

SCK/SCL High Time

Setup Time CDIN to SCK/SCL Rising

(slow mode)

(fast mode)

(slow mode)

(slow mode)

(fast mode)

(slow mode)

(fast mode)

(slow mode)

(fast mode)

(slow mode)

(fast mode)

fsck

fsck

tcss

tr

tf

tf

tscl

tscl

tsch

tsch

tcdisu

-

350 kHz

-

2000

20

-

ns

-

50

ns

-

300

ns

-

50

ns

1100

-

ns

150

-

ns

1100

-

ns

150

-

ns

250

-

ns

50

-

ns

Hold Time SCK/SCL Rising to CDIN

Transition Time from SCK/SCL to CDOUT Valid

Time from SCK/SCL Rising to REQ Rising

Rise Time for REQ

Fall Time for REQ

Hold Time for REQ from SCK/SCL Rising

Time from SCK/SCL Falling to CS Rising

High Time Between Active CS

(Note 6) tcdih

50

-

ns

(Note 7) tscdov

-

40

ns

(Note 7) tscrh

-

200

ns

(Note 8)

trr

-

50

ns

(Note 9)

trf

-

20

ns

(Note 9) tscrl

0

-

ns

tsccsh

20

-

ns

tcsht

200

-

ns

Notes: 6. Data must be held for sufficient time to bridge 300(50) ns transition time of SCK/SCL.

7. CDOUT should NOT be sampled during this time period.

8. REQ will only go HIGH if there is no data in SCPOUT at the rising edge of SCL/SCK during a READ

operation as shown. DSP frequency is 20 MHz. Pull-up resistor is 2 kΩ. CL = 20 pF.

9. If REQ went HIGH as indicated in note 7, then REQ will hold high at least until the next rising edge of

SCK/SCL. If data is in SCPOUT at this time REQ will go active LOW again. This condition should be

treated as a new READ process. Address and R/W bit should be sent again.

8