CS61582 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CS61582 Datasheet PDF : 32 Pages

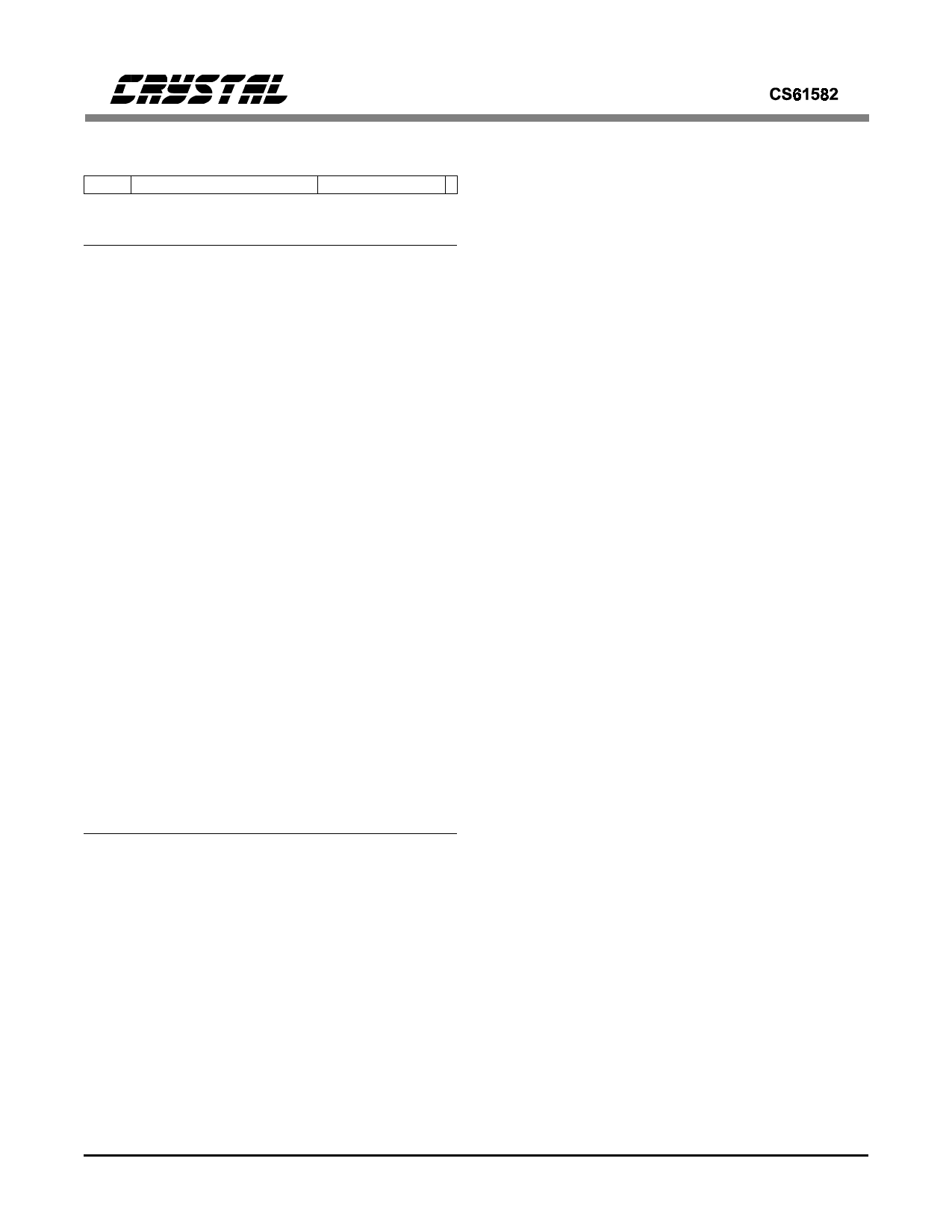

| |||

MSB

LSB

31 28 27

12 11

10

00000000000000000011000011001001

(4 bits)

(16 bits)

(11 bits)

BIT #(s)

31-28

27-12

11-1

0

FUNCTION

Version number

Part Number

Manufacturer Number

Constant Logic ’1’

Total Bits

4

16

11

1

Figure 10. Device Identification Register

Data from the DIR is shifted out to J-TDO LSB

first.

Bypass Register: The Bypass register consists of

a single bit, and provides a serial path between

J-TDI and J-TDO, bypassing the BSR. This al-

lows bypassing specific devices during certain

board-level tests. This also reduces test access

times by reducing the total number of shifts re-

quired from J-TDI to J-TDO.

SAMPLE/PRELOAD Instruction: The SAM-

PLE/PRELOAD instructions allows scanning of

the boundary-scan register without interfering

with the operation of the CS61582. This instruc-

tion connects the BSR to the J-TDI and J-TDO

pins. The normal path between the CS61582

logic and its I/O pins is maintained. The signals

on the I/O pins are loaded into the BSR. Addi-

tionally, this instruction can be used to latch

values into the digital output pins.

IDCODE Instruction: The IDCODE instruction

connects the device identification register to the

J-TDO pin. The IDCODE instruction is forced

into the instruction register during the Test-

Logic-Reset controller state.The default

instruction is IDCODE after a device reset.

BYPASS Instruction: The BYPASS instruction

connects the minimum length bypass register be-

tween the J-TDI and J-TDO pins and allows data

to be shifted in the Shift-DR controller state.

JTAG Instructions and Instruction Register (IR)

The instruction register (2 bits) allows the in-

struction to be shifted into the JTAG circuit. The

instruction selects the test to be performed or the

data register to be accessed or both. The valid

instructions are shifted in LSB first and are listed

below:

IR CODE

00

01

10

11

INSTRUCTION

EXTEST

SAMPLE/PRELOAD

IDCODE

BYPASS

EXTEST Instruction: The EXTEST instruction

allows testing of off-chip circuitry and board-

level interconnect. EXTEST connects the BSR to

the J-TDI and J-TDO pins. The normal path be-

tween the CS61582 logic and I/O pins is broken.

The signals on the output pins are loaded from

the BSR and the signals on the input pins are

loaded into the BSR.

DS224PP1

Internal Testing Considerations

Note that the INTEST instruction is not sup-

ported because of the difficulty in performing

significant internal tests using JTAG.

The one test that could be easily performed us-

ing an arbitrary clock rate on TCLK and

REFCLK is a local loopback with jitter attenu-

ator disabled. However, this test provides limited

fault coverage and is only useful in determining

if the device had been catastrophically destroyed.

Alternatively, catastrophic destruction of the de-

vice and/or surrounding board traces can be

detected using EXTEST. Therefore, the INTEST

instruction provides limited testing capability

and was not included in the CS61582.

JTAG TAP Controller

Figure 11 shows the state diagram for the TAP

state machine. A description of each state fol-

lows. Note that the figure contains two main

branches to access either the data or instruction

15