M36P0R8070E0 データシートの表示(PDF) - Numonyx -> Micron

部品番号

コンポーネント説明

メーカー

M36P0R8070E0 Datasheet PDF : 22 Pages

| |||

Functional description

M36P0R8070E0

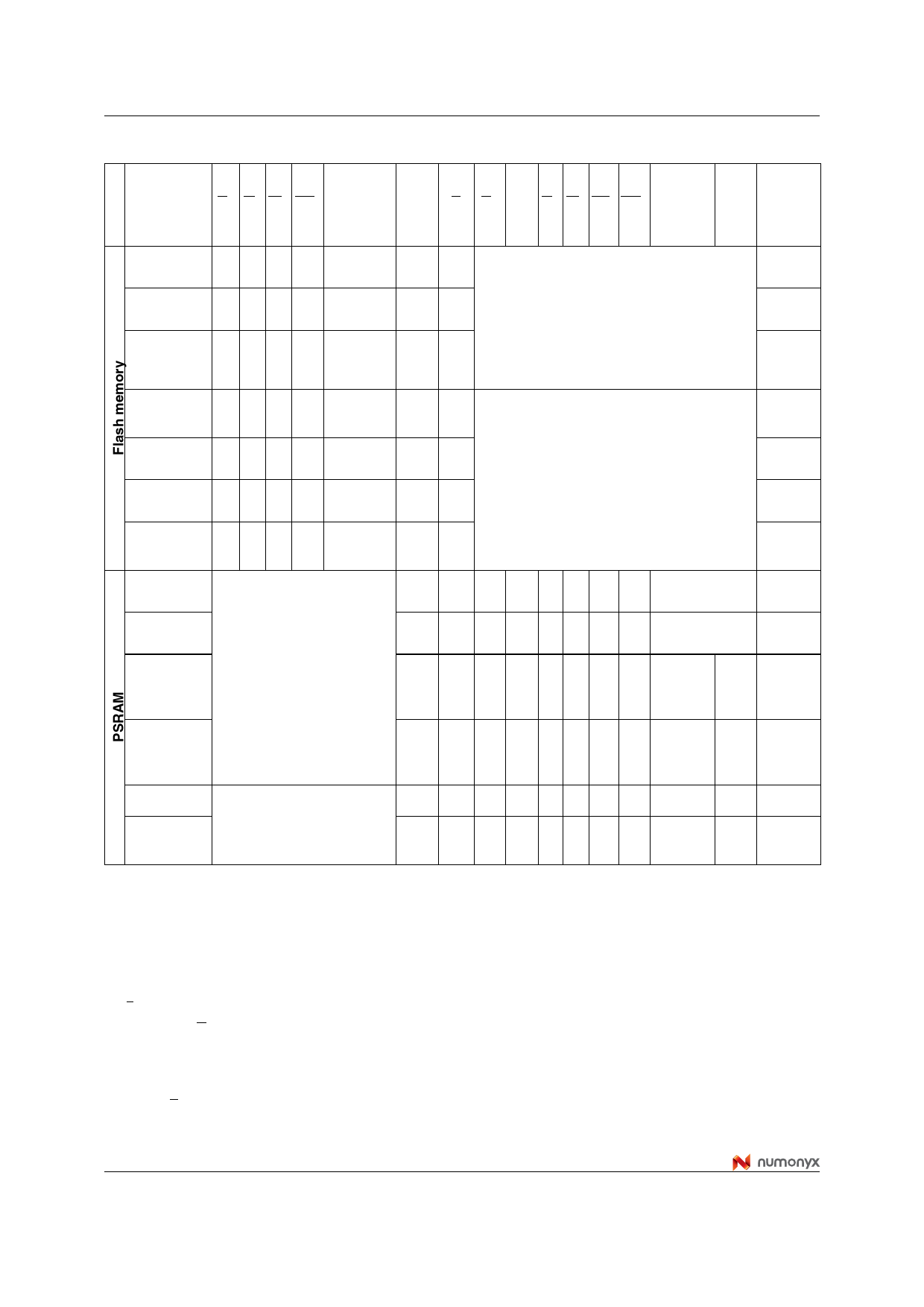

Table 2. Main operating modes(1)

Operation

EF GF WF RPF

DPDF(2)

WAIT

(3)

L

EP CRP GP WP LBP UBP

A18-

A19(4)

A0-

A17

A20-

A22

DQ15-

DQ0

Bus Read

Bus Write

Address

Latch

VIL

VIL

VIH

VIH

de-

asserted(5)

VIL

VIH VIL

VIH

de-

asserted(5)

VIL

X

VIH

VIH

de-

asserted(5)

VIL(6)

Flash

data out

VIL(6)

Only

PSRAM must be disabled.

one Flash memory can be enabled

at

a

Flash

data in

time.

Flash

VIL

data out

or Hi-Z (7)

Output

Disable

VIL VIH VIH

VIH

de-

asserted(5)

Hi-Z

X

Hi-Z

Standby

VIH X

X

VIH

de-

asserted(5)

Hi-Z

X

Any PSRAM mode is allowed.

Hi-Z

Reset

X

X

X

VIL

de-

asserted(5)

Hi-Z

X

Flash memories must be disabled.

Hi-Z

Deep Power-

Down

VIH

X

X

VIH asserted(8) Hi-Z

X

Hi-Z

Read

Low-Z VIL VIL VIL VIL VIH VIL VIL

Valid

Write

Low-Z VIL VIL VIL X VIL VIL VIL

Valid

Read

Flash memories must be

00(RCR)

Configuration

Register

disabled

Low-Z VIL VIL VIH VIL VIH VIL VIL 10(BCR) X

X1(DIDR)

PSRAM

data out

PSRAM

data in

BCR/RC

R/DIDR

contents

Program

Configuration

Register(9)

00(RCR) BCR/

Low-Z VIL VIL VIH X VIH X

X

RCR

10(BCR) data

Hi-Z

Standby

Any Flash memory mode is Hi-Z X VIH VIL X X X X

Hi-Z

allowed. Only one Flash

Deep Power- memory can be enabled at a

Down(10)

time

Hi-Z

X VIH X

XX X

X

Hi-Z

1. X = Don’t Care.

2. The DPDF signal polarity depends on the value of the ECR14 bit.

3. WAIT signal polarity is configured using the Set Configuration Register command. See the M58PR256J datasheet for

details.

4. A18 and A19 are used to select the BCR (Bus Configuration Register), RCR (Refresh Configuration Register) or DIDR

(Device ID Register).

5. If ECR15 is set to '0', the Flash memory device cannot enter the Deep Power-Down mode, even if DPDF is asserted.

6. L can be tied to VIH if the valid address has been previously latched.

7. Depends on GF.

8. ECR15 has to be set to ‘1’ for the Flash memory device to enter Deep Power-Down.

9. BCR and RCR only.

10. Bit 4 of the Refresh Configuration Register must be set to ‘0’, bit 4 (BCR4) of the Bus Configuration Register must be set to

‘0’, and E has to be maintained High, VIH, during Deep Power-Down mode.

14/22