M58MR016C データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M58MR016C Datasheet PDF : 51 Pages

| |||

M58MR016C, M58MR016D

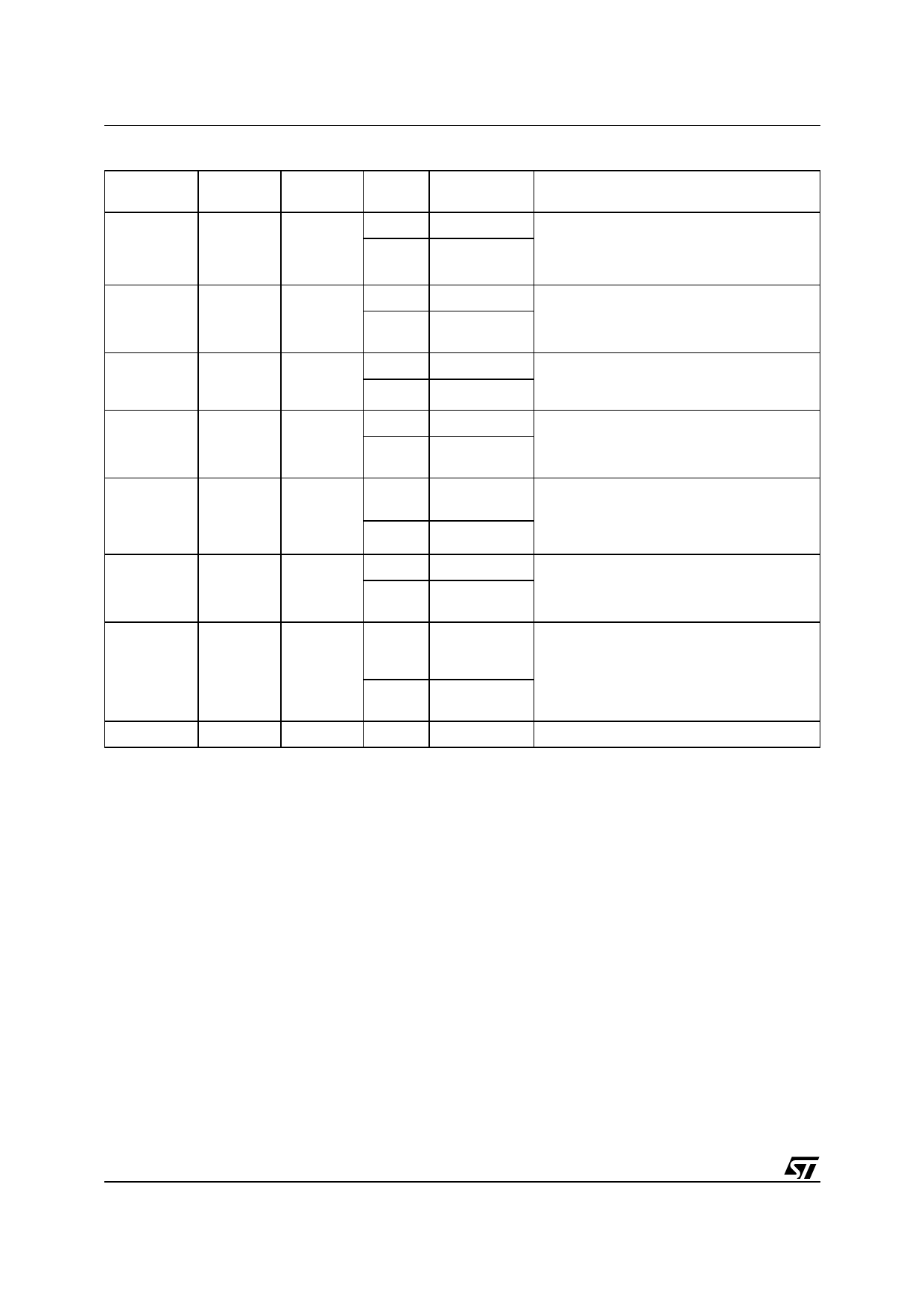

Table 12. Status Register Bits

Mnemonic

Bit

Name

P/ECS

7

P/ECS

Status

ESS

ES

PS

VPPS

6

Erase

Suspend

Status

5

Erase

Status

4

Program

Status

3

VPP Status

PSS

BPS

2

Program

Suspend

Status

1

Block

Protection

Status

0

Reserved

Note: Logic level ’1’ is VIH and ’0’ is VIL.

Logic

Level

Definition

Note

1 Ready

0 Busy

Indicates the P/E.C. status, check during

Program or Erase, and on completion before

checking bits b4 or b5 for Program or Erase

Success.

1 Suspended

On an Erase Suspend instruction P/ECS and

0

In Progress or ESS bits are set to ’1’. ESS bit remains ’1’ until

Completed

an Erase Resume instruction is given.

1 Erase Error

ES bit is set to ’1’ if P/E.C. has applied the

maximum number of erase pulses to the block

0 Erase Success without achieving an erase verify.

1 Program Error

PS bit set to ’1’ if the P/E.C. has failed to

0

Program

Success

program a word.

1

VPP Invalid,

Abort

0

VPP OK

VPPS bit is set if the VPP voltage is below

VPPLK when a Program or Erase instruction is

executed. VPP is sampled only at the beginning

of the erase/program operation.

1 Suspended

On a program Suspend instruction P/ECS and

0

In Progress or PSS bits are set to ’1’. PSS remains ’1’ until a

Completed

Program Resume Instruction is given.

Program/Erase

1

on protected

BPS bit is set to ’1’ if a Program or Erase

Block, Abort operation has been attempted on a protected

0

No operation to block.

protected blocks

must be issued to reset b5, b4, b3 and b1 of the

Status Register.

During the execution of the program by the P/E.C.,

the bank in programming accepts only the RSR

(Read Status Register) and PES (Program/Erase

Suspend) instructions. See Figure 16 for Program

Flowchart and Pseudo Code.

Double Word Program (DPG)

This feature is offered to improve the programming

throughput, writing a page of two adjacent words

in parallel. The first command must be given to the

target block and only one partition can be pro-

grammed at a time; the other partition must be in

one of the read modes or in the erase suspended

mode (see Table 8).

The two words must differ only for the address A0.

Programming should not be attempted when VPP

is not at VPPH. The operation can also be executed

if VPP is below VPPH but result could be uncertain.

These instruction uses three write cycles. The first

command written is the Double Word Program

Set-Up command 30h. A second write operation

latches the Address and the Data of the first word

to be written, the third write operation latches the

Address and the Data of the second word to be

written and starts the P/E.C. (see Table 11).

Read operations in the targeted bank output the

Status Register content after the programming

has started. The Status Register bit b7 returns ’0’

while the programming is in progress and ’1’ when

it has completed. After completion the Status reg-

ister bit b4 returns ’1’ if there has been a Program

Failure. Status register bit b1 returns ’1’ if the user

is attempting to program a protected block. Status

Register bit b3 returns a ’1’ if VPP is below VPPLK.

Any attempt to write a ’1’ to an already pro-

grammed bit will result in a program fail (status

register bit b4 set). (See Table 12).

14/51