M58MR032-ZCT データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M58MR032-ZCT Datasheet PDF : 52 Pages

| |||

M58MR032C, M58MR032D

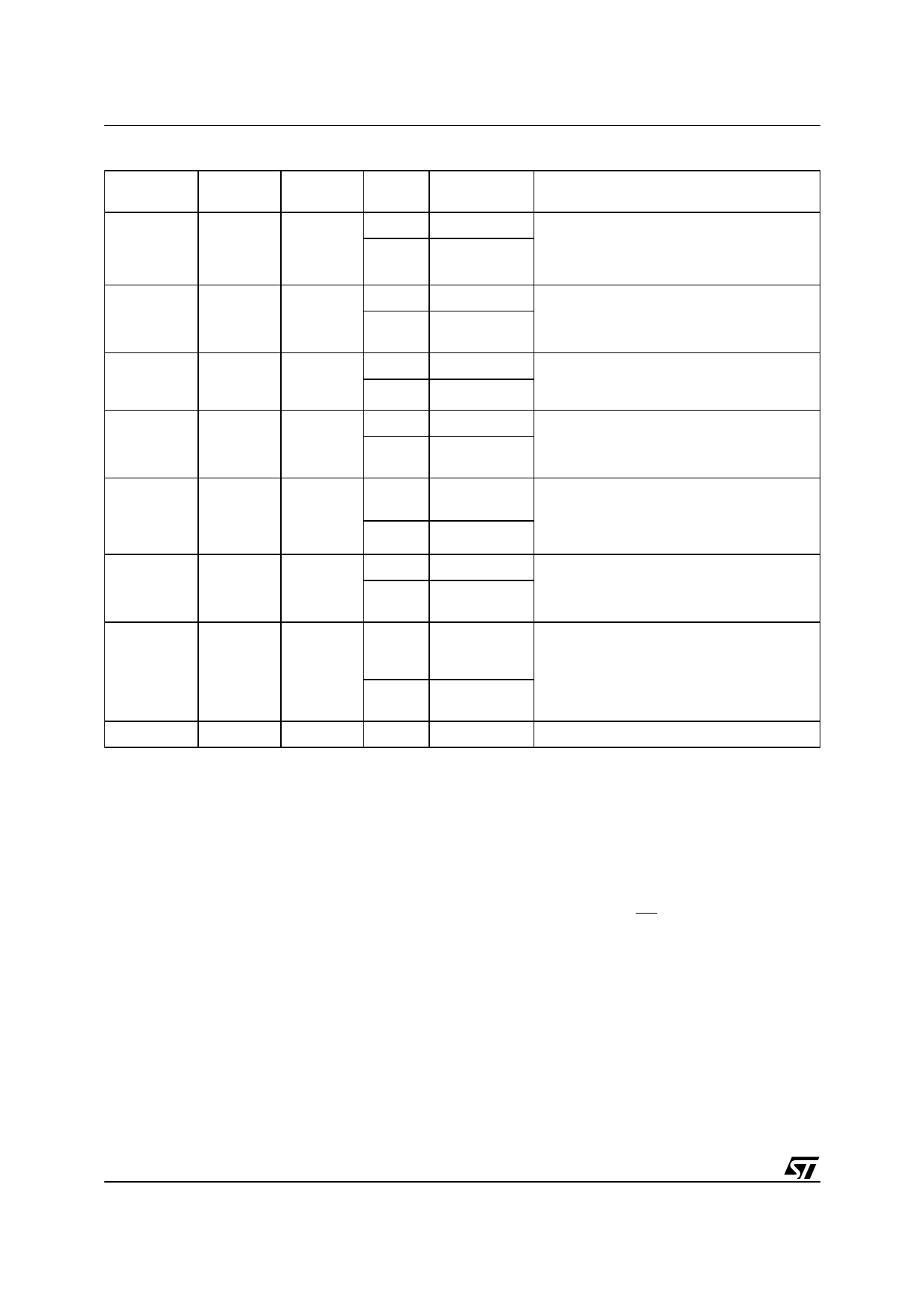

Table 12. Status Register Bits

Mnemonic

Bit

Name

P/ECS

7

P/ECS

Status

ESS

ES

PS

VPPS

6

Erase

Suspend

Status

5

Erase

Status

4

Program

Status

3

VPP Status

PSS

BPS

2

Program

Suspend

Status

1

Block

Protection

Status

0

Reserved

Note: Logic level ’1’ is VIH and ’0’ is VIL.

Logic

Level

Definition

Note

1 Ready

0 Busy

Indicates the P/E.C. status, check during

Program or Erase, and on completion before

checking bits b4 or b5 for Program or Erase

Success.

1 Suspended

On an Erase Suspend instruction P/ECS and

0

In Progress or ESS bits are set to ’1’. ESS bit remains ’1’ until

Completed

an Erase Resume instruction is given.

1 Erase Error

ES bit is set to ’1’ if P/E.C. has applied the

maximum number of erase pulses to the block

0 Erase Success without achieving an erase verify.

1 Program Error

PS bit set to ’1’ if the P/E.C. has failed to

0

Program

Success

program a word.

1

VPP Invalid,

Abort

0

VPP OK

VPPS bit is set if the VPP voltage is below

VPPLK when a Program or Erase instruction is

executed. VPP is sampled only at the beginning

of the erase/program operation.

1 Suspended

On a program Suspend instruction P/ECS and

0

In Progress or PSS bits are set to ’1’. PSS remains ’1’ until a

Completed

Program Resume Instruction is given.

Program/Erase

1

on protected

BPS bit is set to ’1’ if a Program or Erase

Block, Abort operation has been attempted on a protected

0

No operation to block.

protected blocks

Program (PG)

The Program instruction programs the array on a

word-by-word basis. The first command must be

given to the target block and only one partition can

be programmed at a time; the other partition must

be in one of the read modes or in the erase sus-

pended mode (see Table 8).

This instruction uses two write cycles. The first

command written is the Program Set-up command

40h (or 10h). A second write operation latches the

Address and the Data to be written and starts the

P/E.C.

Read operations in the targeted bank output the

Status Register content after the programming

has started.

The Status Register bit b7 returns ’0’ while the pro-

gramming is in progress and ’1’ when it has com-

pleted. After completion the Status register bit b4

returns ’1’ if there has been a Program Failure (see

Table 12). Status register bit b1 returns ’1’ if the

user is attempting to program a protected block.

Status Register bit b3 returns a ’1’ if VPP is below

VPPLK. Any attempt to write a ’1’ to an already pro-

grammed bit will result in a program fail (status

register bit b4 set) if VPP = VPPH and will be ig-

nored if VPP = VPP1.

Programming aborts if RP goes to VIL. As data in-

tegrity cannot be guaranteed when the program

operation is aborted, the block containing the

memory location must be erased and repro-

grammed. A Clear Status Register instruction

must be issued to reset b5, b4, b3 and b1 of the

Status Register.

During the execution of the program by the P/E.C.,

the bank in programming accepts only the RSR

(Read Status Register) and PES (Program/Erase

Suspend) instructions. See Figure 16 for Program

Flowchart and Pseudo Code.

14/52