AN87C196CA18 データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

AN87C196CA18 Datasheet PDF : 30 Pages

| |||

Automotive — 87C196CA 18 MHz Microcontroller

4.4

AC Characteristics

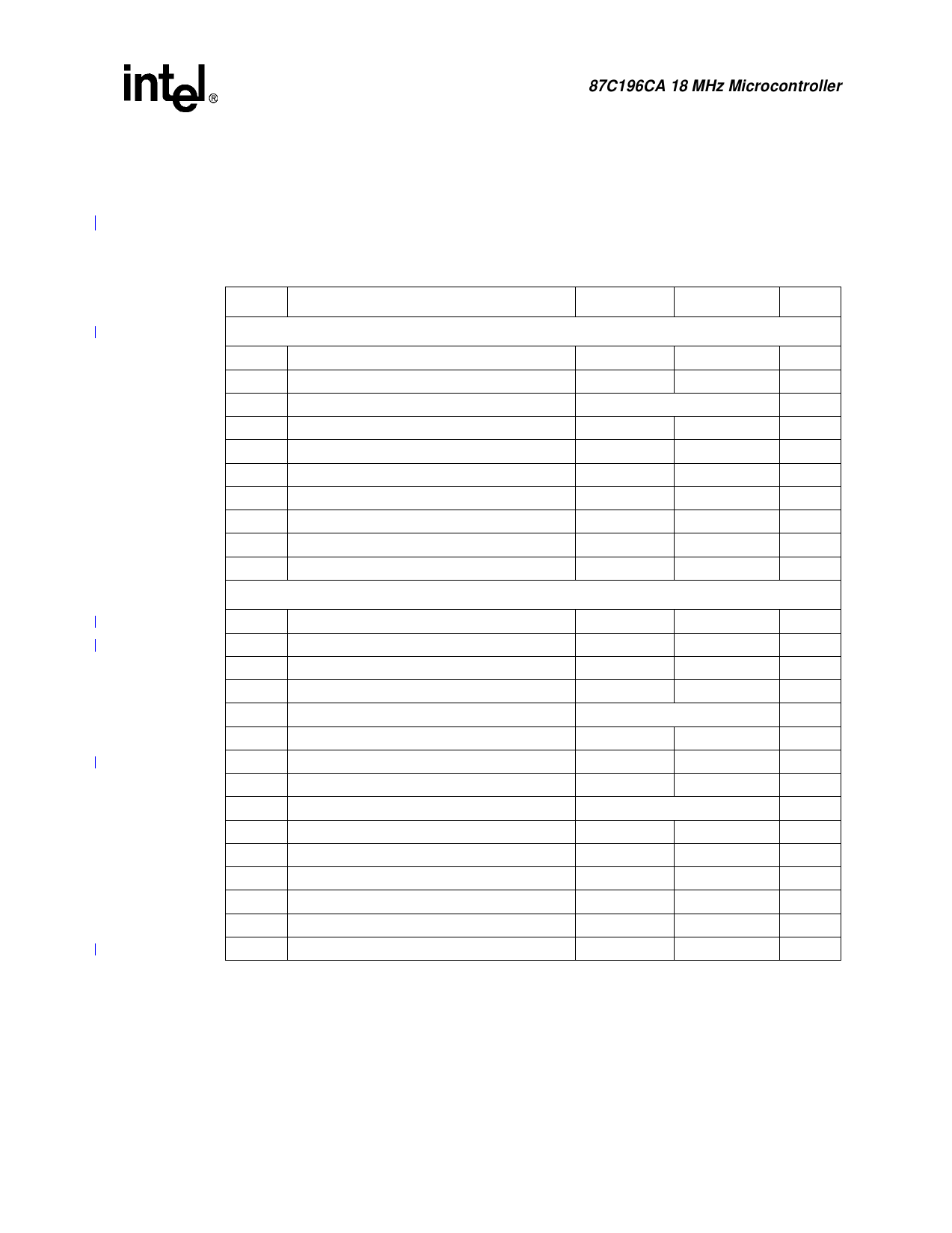

Table 6.

AC Characteristics (Sheet 1 of 2)

(over specified operating conditions); Test conditions: capacitance load on all pins = 100 pF, Rise

and fall times = 10 ns, FOSC = 18 MHz

Symbol

Parameter

Min

Max

Units

The system must meet these specifications to work with the 87C196CA Microcontroller.

TAVYV

TLLYV

TYLYH

TCLYX

TLLYX

TAVDV

TRLDV

TCLDV

TRHDZ

TRXDX

Address Valid to READY Setup

ALE Low to READY Setup

Non Ready Time

READY Hold after CLKOUT Low

READY Hold after ALE Low

Address Valid to Input Data Valid

RD# Active to Input Data Valid

CLKOUT Low to Input Data Valid

End of RD# to Input Data Float

Data Hold after RD# Inactive

The 87C196CA Microcontroller meets these specifications.

2 TOSC – 75

TOSC – 70

No Upper Limit

0

TOSC – 15

0

TOSC – 30

2 TOSC – 40

3 TOSC – 55

TOSC – 22

TOSC – 50

TOSC

ns

ns

ns

ns(1)

ns(1)

ns

ns

ns

ns

ns

FXTAL

Oscillator Frequency

4

18

MHz(2)

TOSC

TXHCH

TOFD

Oscillator Period (1/FXTAL)

XTAL1 High to CLKOUT High or Low

Clock Failure to Reset Pulled Low

55

250

ns

20

110

ns(3)

4

40

µS(7)

TCLCL

CLKOUT Period

2 TOSC

ns

TCHCL CLKOUT High Period

TOSC – 10

TOSC + 15

ns

TCLLH CLKOUT Falling Edge to ALE Rising

–15

10

ns

TLLCH ALE/ADV# Falling Edge to CLKOUT Rising

–20

15

ns

TLHLH

ALE/ADV# Cycle Time

4 TOSC

ns

TLHLL

ALE/ADV# High Period

TOSC – 10

TOSC + 10

ns

TAVLL

Address Setup to ALE/ADV# Falling Edge

TOSC – 15

ns

TLLAX

Address Hold after ALE/ADV# Falling Edge

TOSC – 40

ns

TLLRL

ALE/ADV# Falling Edge to RD# Falling Edge

TOSC – 30

ns

TRLCL

RD# Low to CLKOUT Falling Edge

4

30

ns

TRLRH RD# Low Period

TOSC – 10

ns

NOTES:

1. If max is exceeded, additional wait states will occur.

2. Testing performed at 4 MHz; however, the device is static by design and will typically operate below 1 Hz.

3. Typical specifications, not guaranteed.

4. Assuming back-to-back bus cycles.

5. 8-bit bus only.

6. TRLAZ (max) = 5 ns by design.

7. TOFD is the time for the oscillator fail detect circuit (OFD) to react to a clock failure.

Datasheet

11