UPD75212ACW データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

メーカー

UPD75212ACW Datasheet PDF : 70 Pages

| |||

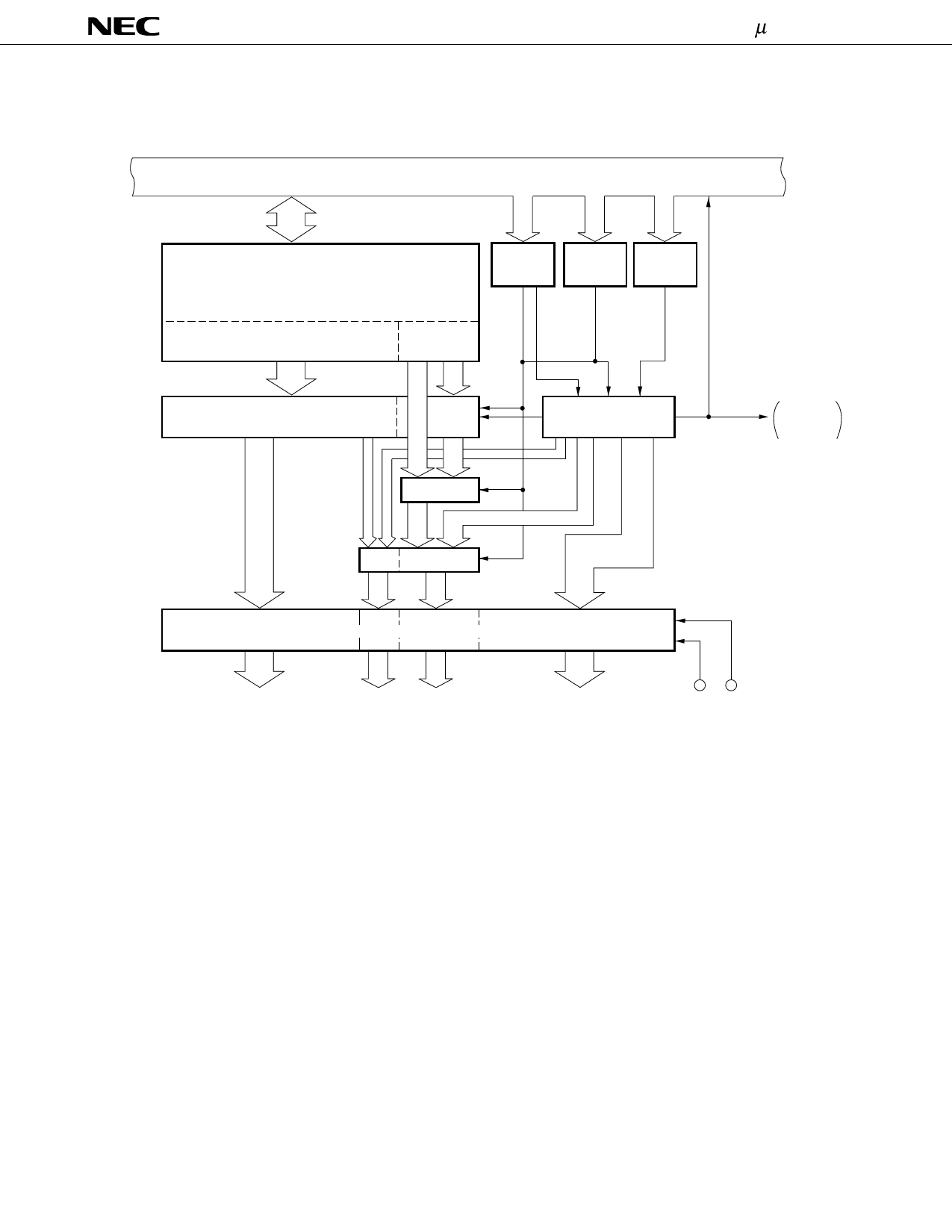

Fig. 5-8 FIP Controller/Driver Block Diagram

µPD75212A

Display Data Memory

(64 × 4 Bits)

Internal Bus

4

4

4

Display

Mode

Register

Digit

Select

Register

Dimmer

Select

Register

Key Scan

Flag (KSF)

Key Scan Registers (KS0, KS1)

12

Segment Data Latch (16)

Port H

4

10

10

S0-S9

44

Selector

22 4 4

Selector

2

4

High-Voltage Output Buffer

2

4

T15/S10, T13/S12/PH0-

T14/S11 T10/S15/PH3

Digit Signal

Generator

INTKS

IRQKS

Generation

Signal

10

10

T0-T9

VLOAD VPRE

Note

The FIP controller/driver can only operate in the high and intermediate-speeds (PCC = 0011B or

0010B) of the main system clock (SCC.0 = 0). It may cause errors with any other clock or in the

standby mode. Thus, be sure to stop FIP controller operation (DSPM.3 = 0) and then shift the unit

to any other clock mode or the standby mode.

26