AD1955 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD1955 Datasheet PDF : 10 Pages

| |||

AD1955

PRELIMINARY TECHNICAL DATA

Serial Data Format in SACD mode

In the SACD mode, the AD1955 supports both normal mode or phase modulation mode, which are selected by Control register 1, bit 6.

If normal mode is selected, DSD_SCLK, DSD_LDATA and DSD_RDATA are used to interface with DSD decoder chip. In this mode,

the DSD data is clocked in the AD1955 using rising edge of DSD_SCLK with 64fs rate, 2.8224MHz. DSD_PHASE pin should be

connected LOW.

If phase modulation mode is selected, DSD_PHASE pin is also used to interface with the DSD decoder. In this mode, a 64fs

DSD_PHASE signal is used as a reference signal to receive the data from the decoder. The DSD data is clocked into the AD1955 with

a 128fs DSD_SCLK.

The AD1955 can operate as a master or slave device. In master mode, the AD1955 will output DSD_SCLK and DSD_PHASE (if in

the phase modulation mode) to a DSD decoder and will support normal mode and Phase modulation mode 0. In slave mode, the

AD1955 will accept DSD_SCLK and DSD_PHASE (if in the phase modulation mode) from a DSD decoder and supports all of the

normal and phase modulation modes.

When the SACD Port is not being used, the SACD pins (6, 7, 8 and 9) should be tied LOW.

Master Clock

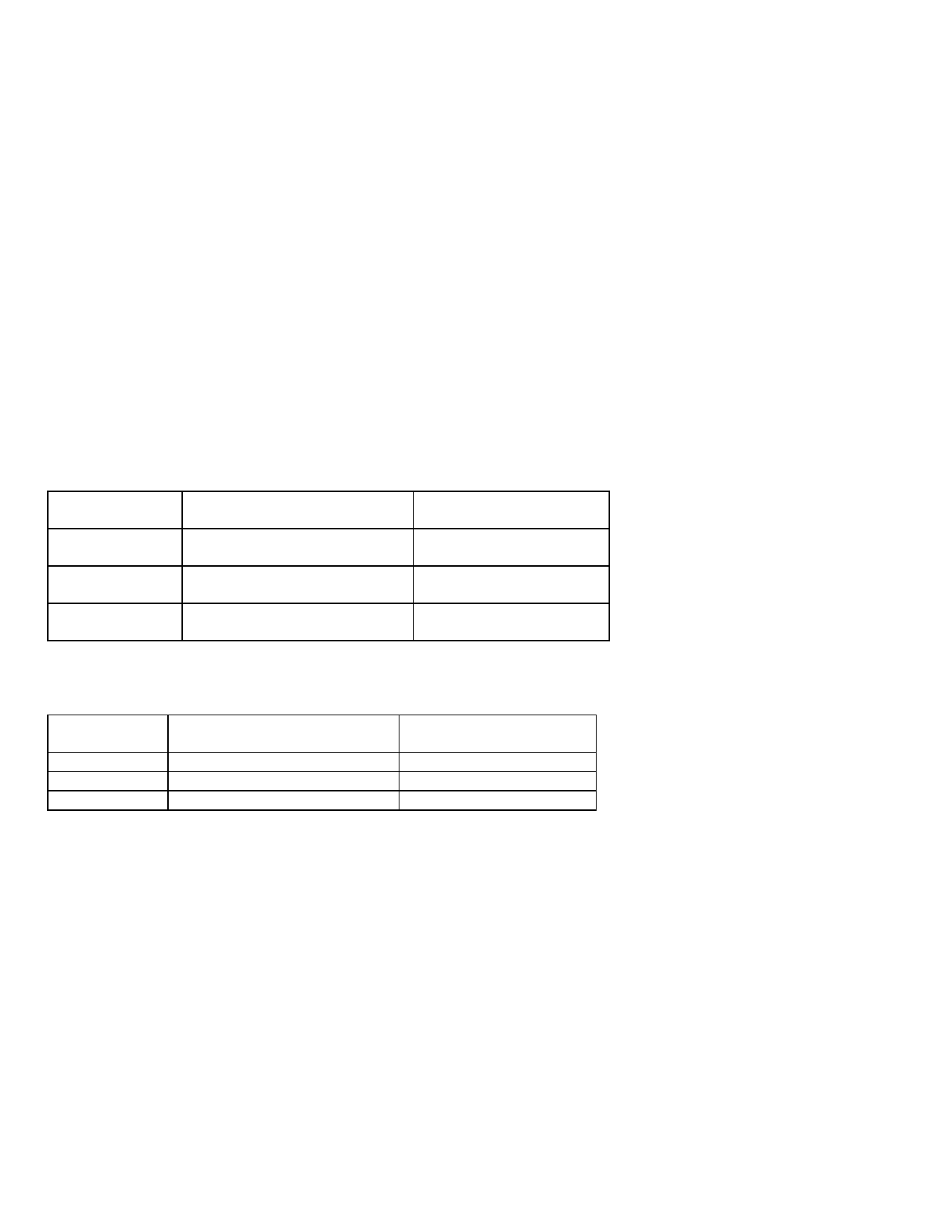

The AD1955 must be set to the proper sample rate and master clock rate using Control Registers 0 and 1. The allowable master clock

frequencies for each interpolation mode are as shown:

Interpolation

Mode

48kHz (INT8X)

Mode

96kHz (INT4X)

Mode

192kHz (INT2X)

Mode

Allowable master clock

frequencies

256*Fs, 384*Fs, 512*Fs,768*Fs

128*Fs, 192*Fs, 256*Fs, 384*Fs

64*Fs, 96*Fs, 128*Fs, 192*Fs

Nominal Input Sample

Rate

32 kHz, 44.1 kHz, 48 KHz

88.2 kHz, 96 KHz

176.4 kHz, 192 KHz

In the External Filter mode, the AD1955 accepts the following master clock frequenies depending on input sample

rate:

Input Data

rate

8fs

4fs

2fs

Allowable master clock

frequencies

256*Fs, 384*fs, 512*Fs,768*Fs

128*Fs, 192*fs, 256*Fs, 384*Fs

64*Fs, 96*fs, 128*Fs, 192*Fs

Nominal Input Sample

Rate (to External Filter)

32 kHz, 44.1 kHz, 48 KHz

88.2 kHz, 96 KHz

176.4 kHz, 192 KHz

In the SACD mode, the AD1955 accepts a 256fs, 512fs and 768fs Master Clock, where fs is nominally 44.1kHz.

Zero Detection

When the AD1955 detects that the audio input data is continuously zero during 1024 LRCLK periods in PCM mode or 8192 LRCLK

periods in 8fs External Digital Filter mode, ZEROL (Pin 21 ) or ZEROR (Pin 20) is set to active.

When the AD1955 is in SACD Mode, it will detect an SACD mute pattern. If the input bit-stream shows a mute pattern for about 22ms,

the AD1955 will set ZEROL(Pin 21 ) or ZEROR(Pin 20) to active. The outputs can be set to active high or low using Control Register

1, bit 8.

Reset/Power Down

The AD1955 will be reset when the RESET pin is set low. The part may be powered down using bit 15, Control Register 0.

-8-

Rev. PrF