AD7175-8 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD7175-8

AD7175-8 Datasheet PDF : 64 Pages

| |||

AD7175-8

Data Sheet

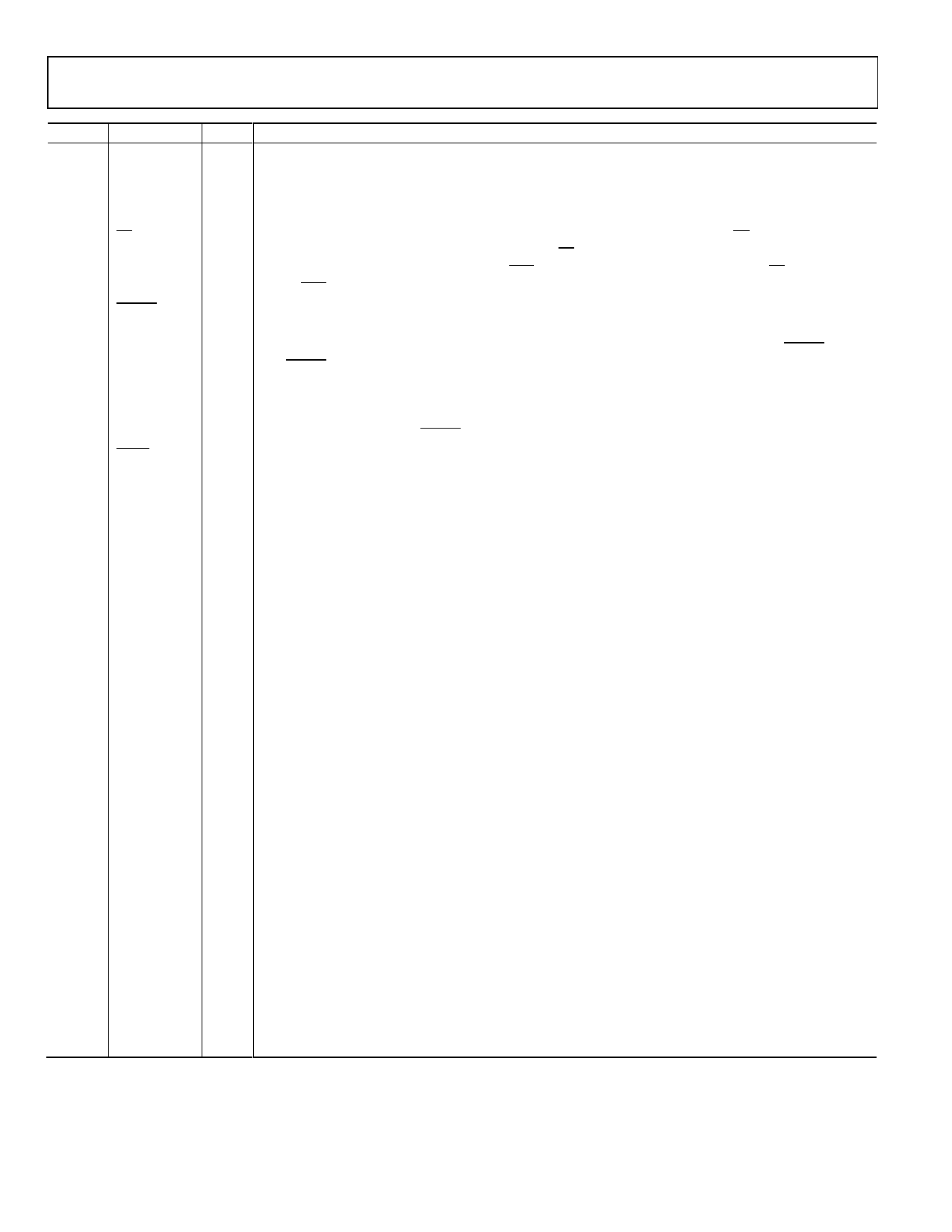

Pin No. Mnemonic

15

DIN

16

SCLK

17

CS

18

ERROR

19

SYNC

20

IOVDD

21

DGND

22

REGCAPD

23

GPIO0

24

GPIO1

25

GPO2

26

AIN4

27

AIN5

28

AIN6

29

AIN7

30

AIN8

31

AIN9

32

AIN10

33

AIN11

34

AIN12

35

AIN13

36

AIN14

37

AIN15

38

GPO3

39

REF−

40

REF+

EP

Type2

DI

DI

DI

DI/O

DI

P

P

AO

DI/O

DI/O

DO

AI

AI

AI

AI

AI

AI

AI

AI

AI

AI

AI

AI

DO

AI

AI

P

Description

Serial Data Input to the Input Shift Register on the ADC. Data in this shift register is transferred to the

control registers in the ADC, with the register address (RA) bits of the communications register

identifying the appropriate register. Data is clocked in on the rising edge of SCLK.

Serial Clock Input. This serial clock input is for data transfers to and from the ADC. SCLK has a Schmitt

triggered input, making the interface suitable for opto-isolated applications.

Chip Select Input. This pin is an active low logic input used to select the ADC. Use CS to select the ADC in

systems with more than one device on the serial bus. CS can be hardwired low, allowing the ADC to operate

in 3-wire mode with SCLK, DIN, and DOUT/RDY used to interface with the device. When CS is high, the

DOUT/RDY output is tristated.

Error input/output or General-Purpose Output. This pin can be used in one of the following three modes:

Active low error input mode. This mode sets the ADC_ERROR bit in the STATUS register.

Active low, open-drain error output mode. The status register error bits are mapped to the ERROR pin.

The ERROR pins of multiple devices can be wired together to a common pull-up resistor so that an error

on any device can be observed.

General-purpose output mode. The status of the pin is controlled by the ERR_DAT bit in the GPIOCON register.

The pin is referenced between IOVDD and DGND, as opposed to the AVDD1 and AVSS levels used by the

GPIO1 and GPIO2 pins. The ERROR pin has an active pull-up circuit in this case.

Synchronization Input. Allows synchronization of the digital filters and analog modulators when using

multiple AD7175-8 devices.

Digital I/O Supply Voltage. The IOVDD voltage ranges from 2 V to 5 V (nominal). IOVDD is independent of

AVDD1 and AVDD2. For example, IOVDD can be operated at 3.3 V when AVDD1 or AVDD2 equals 5 V, or

vice versa. If AVSS is set to −2.5 V, the voltage on IOVDD must not exceed 3.6 V.

Digital Ground.

Digital LDO Regulator Output. This pin is for decoupling purposes only. Decouple this pin to DGND

using a 1 µF capacitor.

General-Purpose Input/Output 0. Logic input/output on this this pin is referred to the AVDD1 and AVSS

supplies.

General-Purpose Input/Output 2. Logic input/output on this this pin is referred to the AVDD1 and AVSS

supplies.

General-Purpose Output 2. Logic output on this this pin is referred to the AVDD1 and AVSS supplies.

Analog Input 4. This pin is selectable through the crosspoint multiplexer.

Analog Input 5. This pin is selectable through the crosspoint multiplexer.

Analog Input 6. This pin is selectable through the crosspoint multiplexer.

Analog Input 7. This pin is selectable through the crosspoint multiplexer.

Analog Input 8. This pin is selectable through the crosspoint multiplexer.

Analog Input 9. This pin is selectable through the crosspoint multiplexer.

Analog Input 10. This pin is selectable through the crosspoint multiplexer.

Analog Input 11. This pin is selectable through the crosspoint multiplexer.

Analog Input 12. This pin is selectable through the crosspoint multiplexer.

Analog Input 13. This pin is selectable through the crosspoint multiplexer.

Analog Input 14. This pin is selectable through the crosspoint multiplexer.

Analog Input 15. This pin is selectable through the crosspoint multiplexer.

General-Purpose Output 3. Logic output on this this pin is referred to the AVDD1 and AVSS supplies.

Reference 1 Input Negative Terminal. REF− can span from AVSS to AVDD1 − 1 V. Reference 1 can be

selected through the REF_SELx bits in the setup configuration registers.

Reference 1 Input Positive Terminal. An external reference can be applied between REF+ and REF−. REF+

can span from AVDD1 to AVSS + 1 V. Reference 1 can be selected through the REF_SELx bits in the setup

configuration registers.

Exposed Pad. Solder the exposed pad to a similar pad on the PCB under the exposed pad to confer

mechanical strength to the package and for heat dissipation. The exposed pad must be connected to AVSS

through this pad on the PCB.

1 Note that, throughout this data sheet, the dual function pin names are referenced by the relevant function only.

2 AI = analog input, AO = analog output, P = power supply, DI = digital input, DO = digital output, and DI/O = bidirectional digital input/output.

Rev. 0 | Page 10 of 64