STV0118 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

STV0118 Datasheet PDF : 42 Pages

| |||

STV0118

II - PIN INFORMATION (continued)

II.2 - Pin Description (continued)

Pin Name

24 CKREF

25 RESET

26

SCL

27

SDA

28 VSYNC/

ODDEVEN

Type

I

I

I

I/O

I/O

Function

Master clock reference signal.

Its rising edge is the default reference for set-up and hold times of all inputs, and for

propagation delay of all outputs (except for SDA output).

CKREF nominal frequency is 27MHz (CCIR601) : input pad with pull down (50kΩ Typ.)

Hardware reset, active LOW.

It has priority over software reset. NRESET imposes default states (see Register Contents).

Minimum Low level required duration is 5 CKREF periods : input pad with pull down

(50kΩ Typ.)

I2C bus clock line (internal 5-bit majority logic with CKREF for reference) : input pad with

pull down (50kΩ Typ.)

I2C bus serial data line.

Input : internal 5-bit majority logic with CKREF for reference

Output : open drain

Frame sync signal :

- input in slave modes, except when sync is extracted from YCrCb data

- output in master mode and when sync is extracted from YCrCb data

- synchronous to rising edge of CKREF

- ODDEVEN default polarity :

odd (not-top) field : LOW level

even (bottom) field : HIGH level

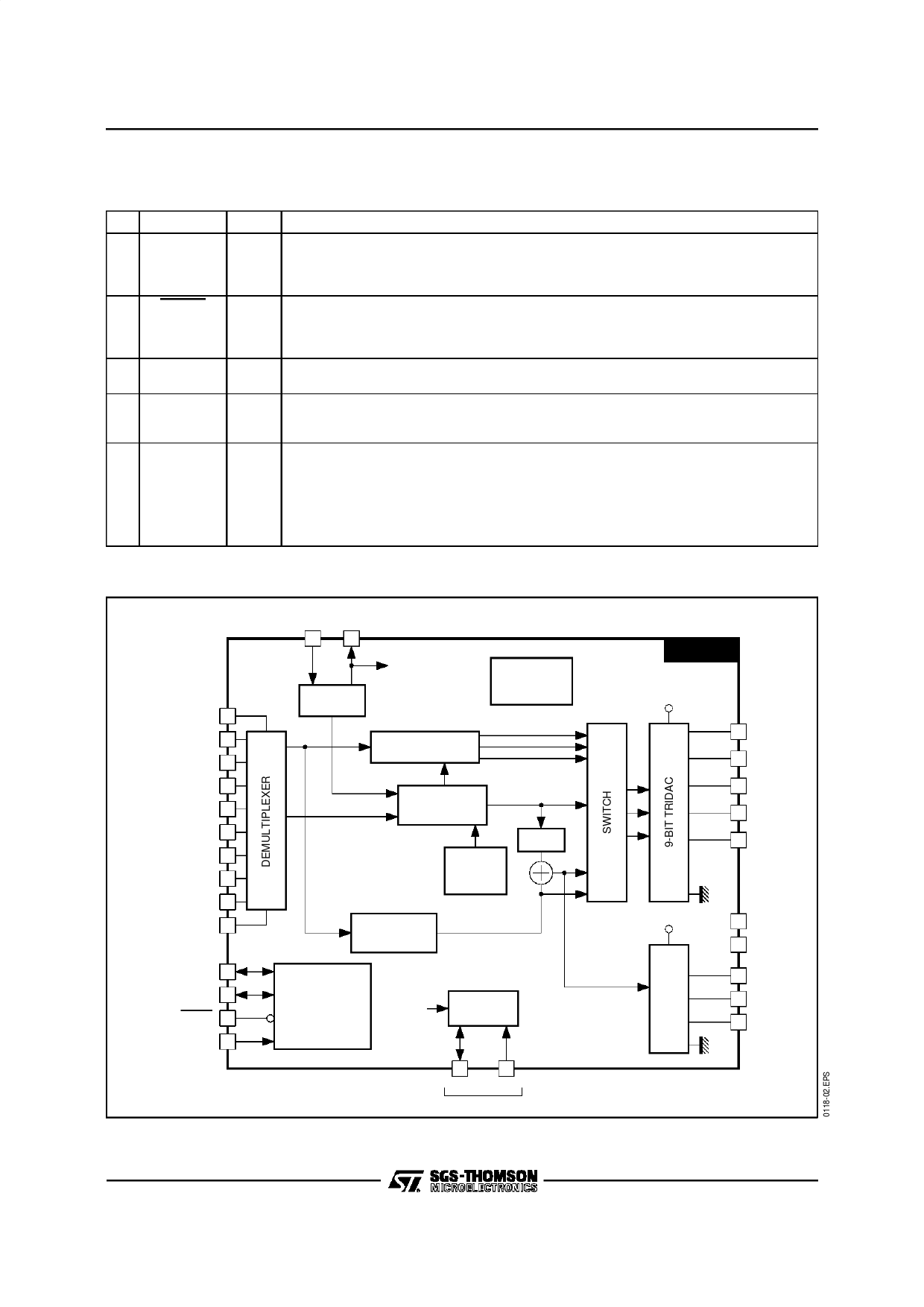

III - BLOCK DIAGRAM

VDD 21

YCRCB7 2

YCRCB6 3

YCRCB5 4

YCRCB4 5

YCRCB3 6

YCRCB2 7

YCRCB1 8

YCRCB0 9

VSS 10

TTXD

23

TTXS/

CSI2C

22

CSI2C

TTXS

TELETEXT

AUTOTEST

COLOR BAR

PATTERN

CB-CR

RGB ENCODING

LUMA

Y

PROCESSING

CLOSED

CAPTIONS

CGMS

TRAP

CHROMA

PROCESSOR

VSYNC/ODDEVEN 28

HSYNC 1

RESET 25

CKREF 24

SYNC CONTROL

& VIDEO TIMING

GENERATOR

CSI2C

CTRL + CFG

REGISTER

27

26

SDA SCL

I2C BUS

STV0118

VDDA

20 G/Y

19 R/C

18 B/CVBS

17 VR_RGB

16 IREF(RGB)

VDDA

9-BIT

DAC

VSSA

14 VSSA

15 VDDA

11 CVBS

12 VR_CVBS

13 IREF(CVBS)

VSSA

5/42