BCM2835 データシートの表示(PDF) - Broadcom Corporation

部品番号

コンポーネント説明

メーカー

BCM2835 Datasheet PDF : 205 Pages

| |||

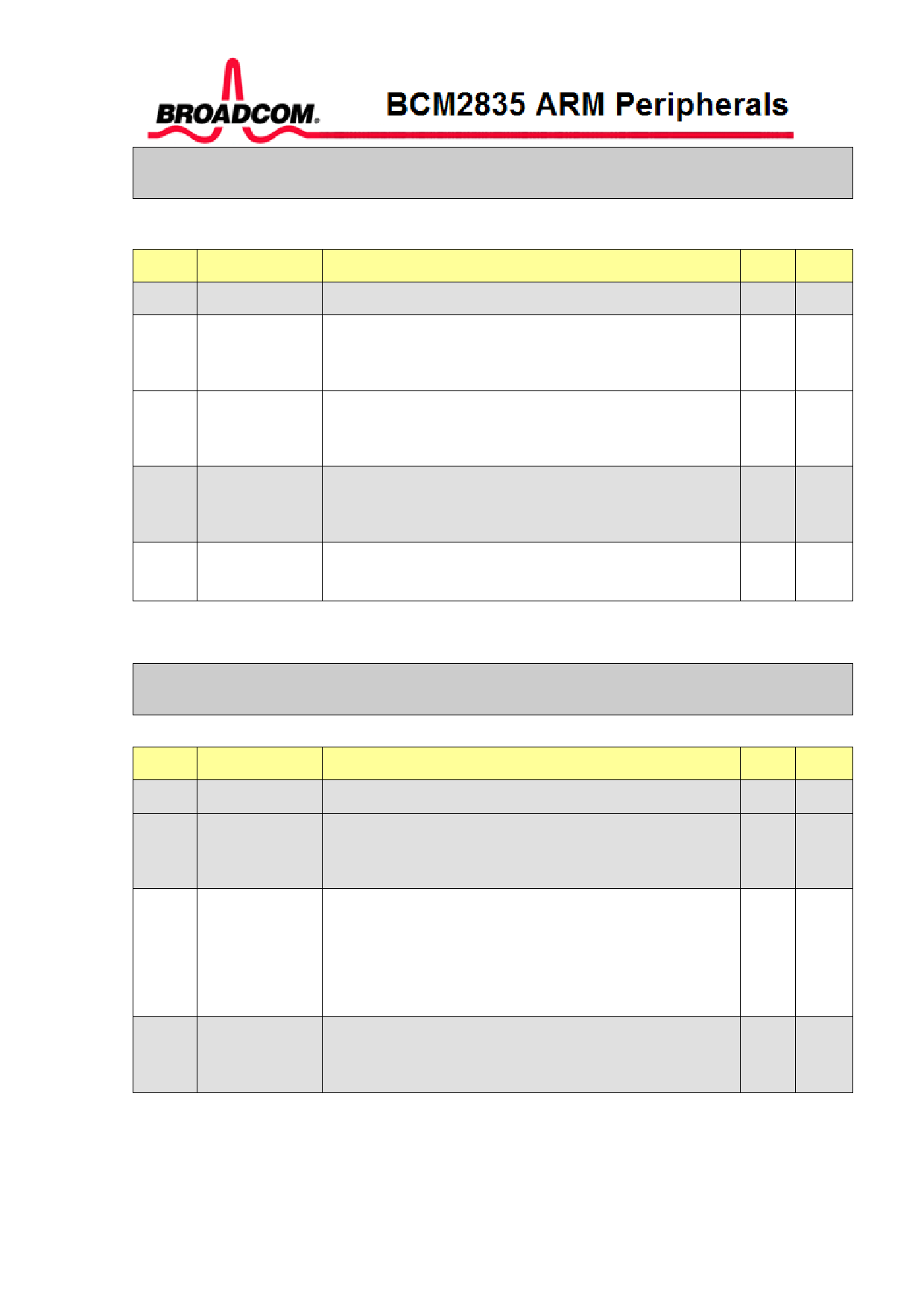

AUX_MU_LCR_REG Register (0x7E21 504C)

SYNOPSIS The AUX_MU_LCR_REG register controls the line data format and gives access to the

baudrate register

Bit(s)

31:8

7

6

5:1

0

Field Name

DLAB access

Break

data size

Description

Type Reset

Reserved, write zero, read as don’t care

If set the first to Mini UART register give access the R/W 0

the Baudrate register. During operation this bit must

be cleared.

If set high the UART1_TX line is pulled low

R/W 0

continuously. If held for at least 12 bits times that will

indicate a break condition.

Reserved, write zero, read as don’t care

Some of these bits have functions in a 16550

0

compatible UART but are ignored here

If clear the UART works in 7-bit mode

If set the UART works in 8-bit mode

R/W 0

AUX_MU_MCR_REG Register (0x7E21 5050)

SYNOPSIS The AUX_MU_MCR_REG register controls the 'modem' signals.

Bit(s) Field Name

31:8

7:2

1

RTS

0

Description

Reserved, write zero, read as don’t care

Reserved, write zero, read as don’t care

Some of these bits have functions in a 16550

compatible UART but are ignored here

If clear the UART1_RTS line is high

If set the UART1_RTS line is low

This bit is ignored if the RTS is used for auto-flow

control. See the Mini Uart Extra Control register

description)

Reserved, write zero, read as don’t care

This bit has a function in a 16550 compatible UART

but is ignored here

Type Reset

0

R/W 0

0

06 February 2012 Broadcom Europe Ltd. 406 Science Park Milton Road Cambridge CB4 0WW

© 2012 Broadcom Corporation. All rights reserved

Page 14