BCM2835 データシートの表示(PDF) - Broadcom Corporation

部品番号

コンポーネント説明

メーカー

BCM2835 Datasheet PDF : 205 Pages

| |||

2.3 Universal SPI Master (2x)

The two universal SPI masters are secondary low throughput5 SPI interfaces. Like the UART

the devices needs to be enabled before they can be used. Each SPI master has the following

features:

• Single beat bit length between 1 and 32 bits.

• Single beat variable bit length between 1 and 24 bits

• Multi beat infinite bit length.

• 3 independent chip selects per master.

• 4 entries 32-bit wide transmit and receive FIFOs.

• Data out on rising or falling clock edge.

• Data in on rising or falling clock edge.

• Clock inversion (Idle high or idle low).

• Wide clocking range.

• Programmable data out hold time.

• Shift in/out MS or LS bit first

A major issue with an SPI interface is that there is no SPI standard in any form. Because the

SPI interface has been around for a long time some pseudo-standard rules have appeared

mostly when interfacing with memory devices. The universal SPI master has been developed

to work even with the most 'non-standard' SPI devices.

2.3.1 SPI implementation details

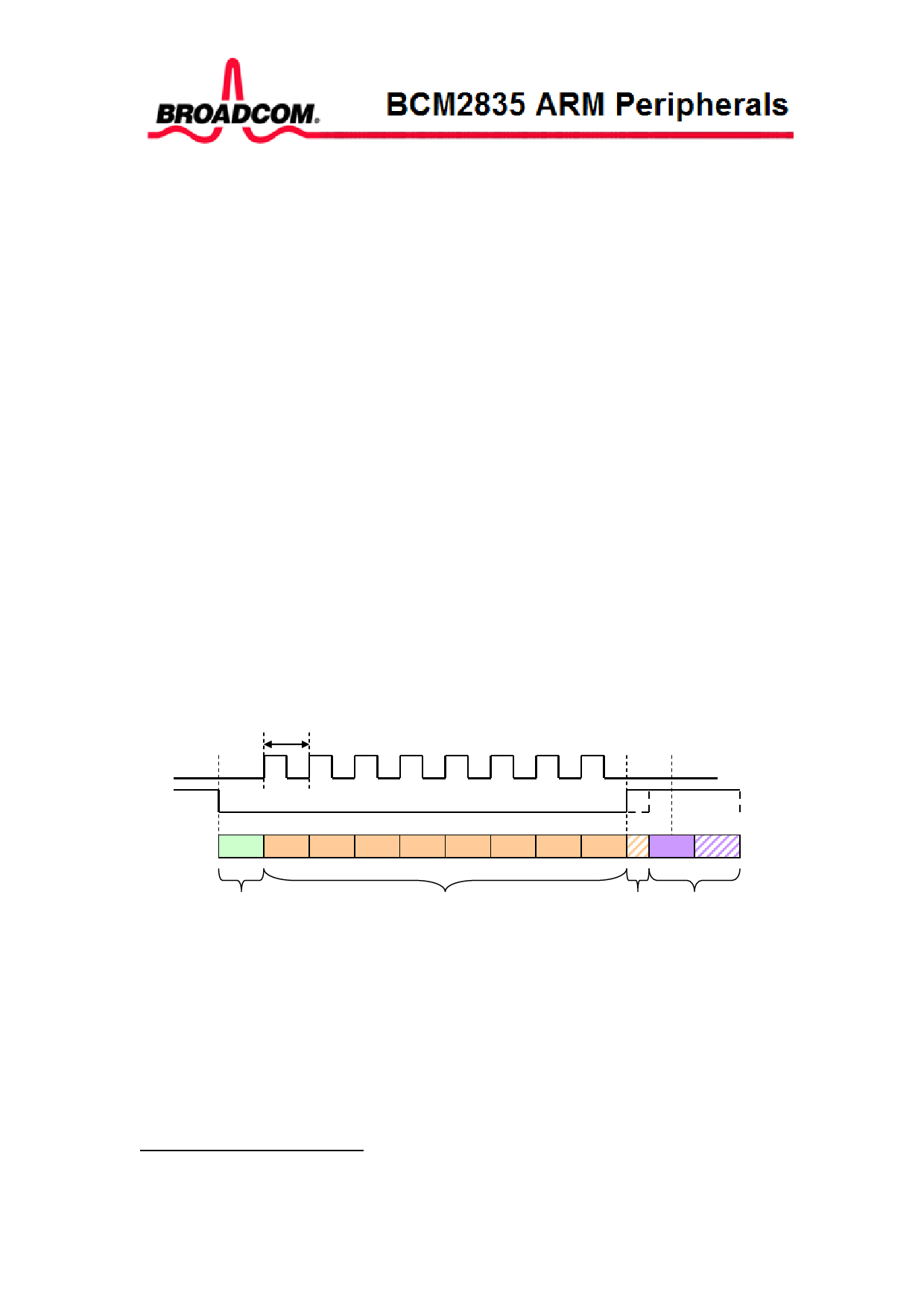

The following diagrams shows a typical SPI access cycle. In this case we have 8 SPI clocks.

1 Bit time

Clk

Cs_n

Set-up

Operate

Hold

Idle

(optional)

One bit time before any clock edge changes the CS_n will go low. This makes sure that the

MOSI signal has a full bit-time of set-up against any changing clock edges.

The operation normally ends after the last clock cycle. Note that at the end there is one half-

bit time where the clock does not change but which still is part of the operation cycle.

There is an option to add a half bit cycle hold time. This makes sure that any MISO data has

at least a full SPI bit time to arrive. (Without this hold time, data clocked out of the SPI

device on the last clock edge would have only half a bit time to arrive).

5 Again the SPIs themselves have no throughput limitations in fact they can run with an SPI clock of 125 MHz.

But doing so requires significant CPU involvement as they have shallow FIFOs and no DMA support.

06 February 2012 Broadcom Europe Ltd. 406 Science Park Milton Road Cambridge CB4 0WW

© 2012 Broadcom Corporation. All rights reserved

Page 20