AD9139(Rev0) データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9139 Datasheet PDF : 56 Pages

| |||

AD9139

The frame clock resets the FIFO in multiple AD9139 devices.

The frame can be either a one shot or continuous clock. In either

case, the pulse width of the frame must be longer than one DCI

cycle in the word mode and two DCI cycles in the byte mode.

When the frame is a continuous clock, fFRAME, ensure that it is

1/8 × fDCI or slower by a factor of 2n, n being an integer (1, 2,

3…). One shot frame reset is the recommended method. Because

the DCI and the DAC clock are generated in two separate clock

domains, timing drifts between the two clocks can cause the FIFO

level to toggle between two values in the continuous reset mode

and, thus, to corrupt the DAC output. Table 19 lists the

requirements of the frame clock in various conditions.

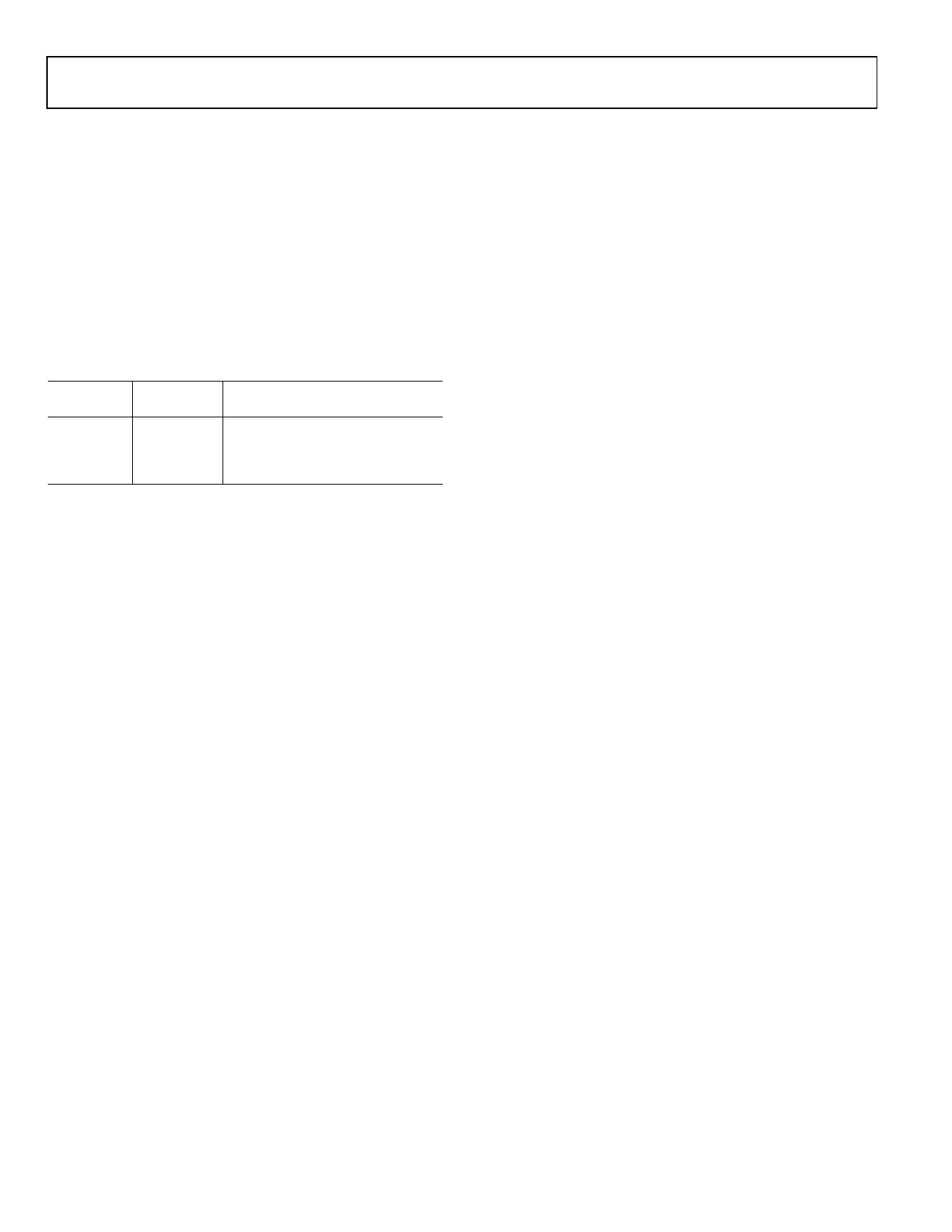

Table 19. Frame Clock Speed and Pulse Width Requirement

Maximum

Sync Clock Speed

Minimum Pulse Width

One Shot N/A1

For both one shot and continuous

Continuous fDCI/8

sync clocks, word mode = one DCI

cycle, and byte mode = two DCI

cycles.

1 N/A means not applicable.

Data Sheet

SYNCHRONIZATION PROCEDURES

When the sync accuracy of an application is less precise than

two DAC clock cycles, it is recommended to turn off the

synchronization machine because no additional steps are required,

other than the regular start-up procedure sequence.

For applications that require more precise sync accuracy than

two DAC clock cycles, use the procedures in the following

sections to set up the system and configure the device.

Rev. 0 | Page 30 of 56