CDB53L21 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

メーカー

CDB53L21 Datasheet PDF : 66 Pages

| |||

CS53L21

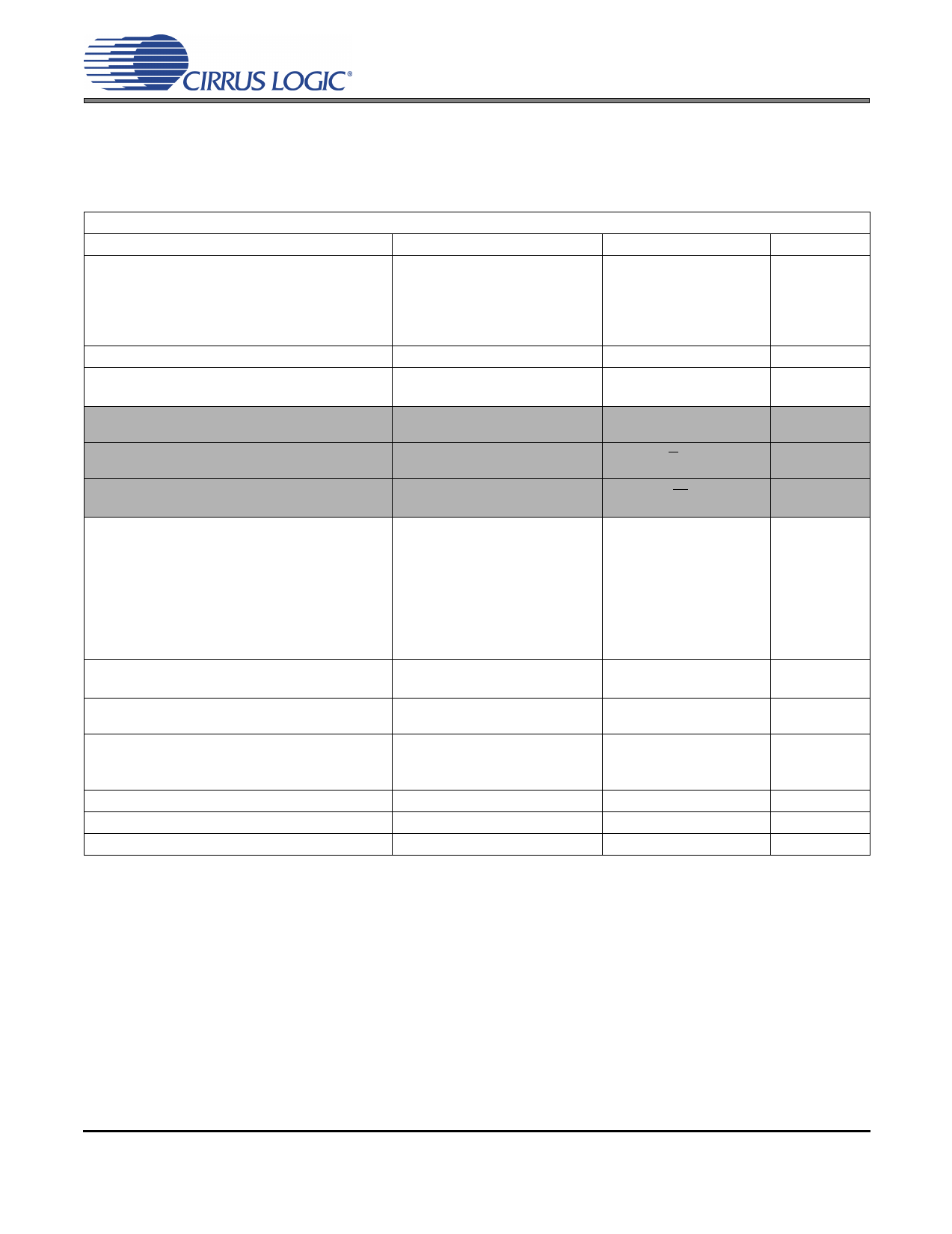

4.2 Hardware Mode

A limited feature-set is available when the A/D powers up in Hardware Mode (see “Recommended Power-

Up Sequence” on page 32) and may be controlled via stand-alone control pins. Table 2 shows a list of func-

tions/features, the default configuration and the associated stand-alone control available.

Hardware Mode Feature/Function Summary

Feature/Function

Default Configuration Stand-Alone Control

Power Control

Device

Powered Up

PGAx

Powered Up

ADCx

Powered Up

-

MIC Bias

Powered Down

MICx Pre-Amplifier

Powered Down

Auto-Detect

Enabled

-

Speed Mode

Serial Port Slave

Serial Port Master

Auto-Detect Speed Mode

Single-Speed Mode

-

MCLK Divide

(Selectable)

“MCLKDIV2” pin 2

Serial Port Master / Slave Selection

(Selectable)

Interface Control

ADC

(Selectable)

ADC Volume & Gain

ADCx High-Pass Filter

ADCx High-Pass Filter Freeze

Line/MIC Input Select

ADC mix Volume and Gain

Signal Processing Engine (SPE)

Data Selection (SPE Enable)

Channel Swap

Digital Boost

Soft Ramp

Zero Cross

Invert

PGAx

Attenuator

ALC

Noise Gate

Invert

Soft Ramp

Zero Cross

MIX

Disabled

Disabled

Disabled

Disabled

0 dB

0 dB

Disabled

Disabled

Enabled

Continuous DC Subtraction

AIN1A to PGAA

AIN1B to PGAB

Disabled

Enabled

Enabled

Disabled

ADC Data to SPE

ADC

ADCA = L; ADCB = R

Table 2. Hardware Mode Feature Summary

“M/S” pin 29

“I²S/LJ” pin 3

-

-

-

-

-

-

-

Note

-

-

-

see Section

4.5 on page 29

see Section

4.5 on page 29

see Section

4.6 on page 31

-

-

-

-

-

-

-

DS700PP1

21