INTEL386 データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

INTEL386 Datasheet PDF : 102 Pages

| |||

Intel386TM SX MICROPROCESSOR

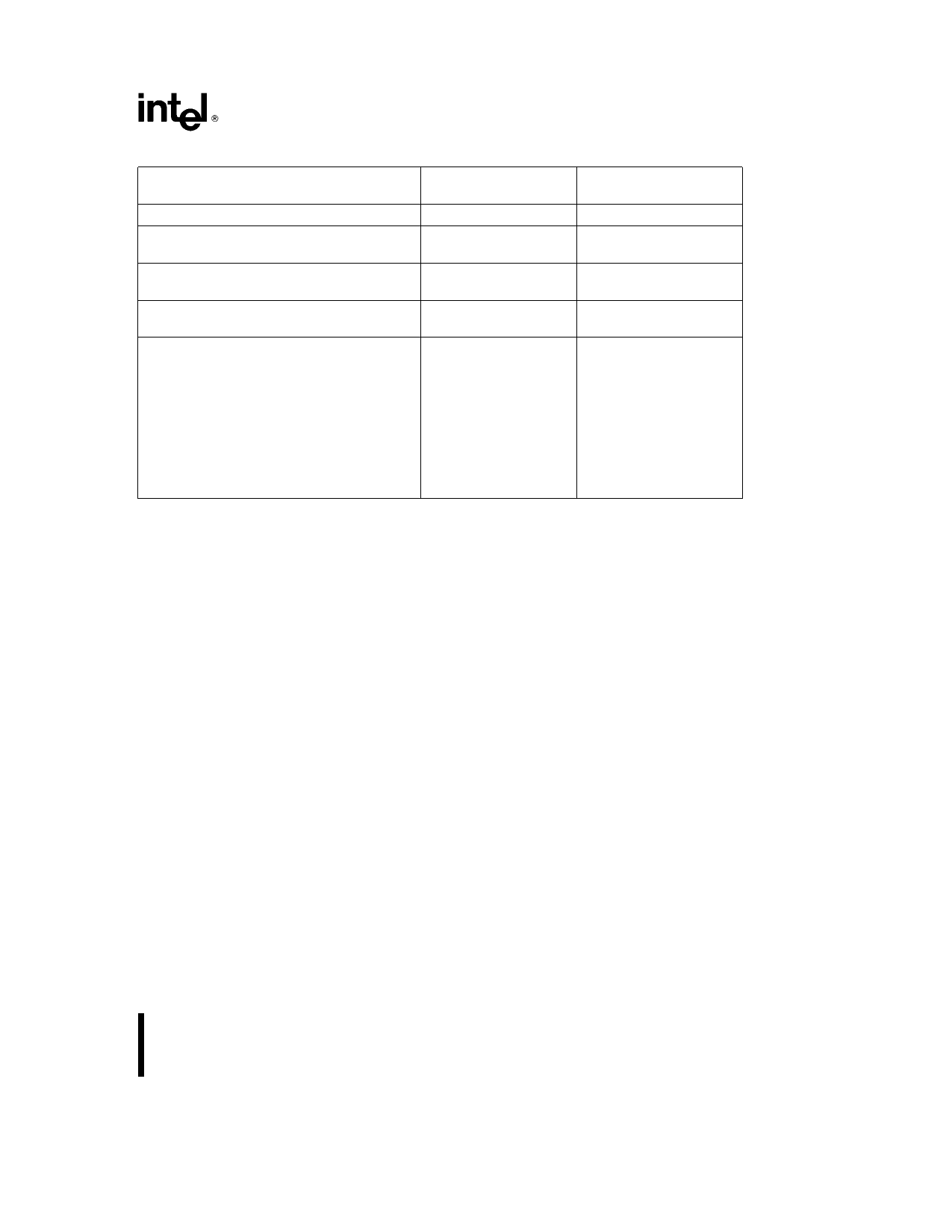

Table 2 3 Segment Register Selection Rules

Type of

Memory Reference

Implied (Default)

Segment Use

Code Fetch

CS

Destination of PUSH PUSHF INT

CALL PUSHA Instructons

SS

Source of POP POPA POPF IRET

RET Instructions

SS

Destination of STOS MOVE REP STOS

and REP MOVS instructions

ES

Other data references with effective

address using base register of

EAX

DS

EBX

DS

ECX

DS

EDX

DS

ESI

DS

EDI

DS

EBP

SS

ESP

SS

Segment Override

Prefixes Possible

None

None

None

None

CS SS ES FS GS

CS SS ES FS GS

CS SS ES FS GS

CS SS ES FS GS

CS SS ES FS GS

CS SS ES FS GS

CS DS ES FS GS

CS DS ES FS GS

32-BIT MEMORY ADDRESSING MODES

The remaining 6 modes provide a mechanism for

specifying the effective address of an operand The

linear address consists of two components the seg-

ment base address and an effective address The

effective address is calculated by summing any

combination of the following three address elements

(see Figure 2 3)

DISPLACEMENT an 8 16 or 32-bit immediate val-

ue following the instruction

BASE The contents of any general purpose regis-

ter The base registers are generally used by compil-

ers to point to the start of the local variable area

INDEX The contents of any general purpose regis-

ter except for ESP The index registers are used to

access the elements of an array or a string of char-

acters The index register’s value can be multiplied

by a scale factor either 1 2 4 or 8 The scaled index

is especially useful for accessing arrays or struc-

tures

Combinations of these 3 components make up the 6

additional addressing modes There is no perform-

ance penalty for using any of these addressing com-

binations since the effective address calculation is

pipelined with the execution of other instructions

The one exception is the simultaneous use of Base

and Index components which requires one addition-

al clock

As shown in Figure 2 4 the effective address (EA) of

an operand is calculated according to the following

formula

EA e BaseRegister a (IndexRegister scaling)

a Displacement

1 Direct Mode The operand’s offset is contained

as part of the instruction as an 8 16 or 32-bit

displacement

2 Register Indirect Mode A BASE register con-

tains the address of the operand

3 Based Mode A BASE register’s contents are

added to a DISPLACEMENT to form the oper-

and’s offset

4 Scaled Index Mode An INDEX register’s con-

tents are multiplied by a SCALING factor and the

result is added to a DISPLACEMENT to form the

operand’s offset

5 Based Scaled Index Mode The contents of an

INDEX register are multiplied by a SCALING fac-

tor and the result is added to the contents of a

BASE register to obtain the operand’s offset

6 Based Scaled Index Mode with Displacement

The contents of an INDEX register are multiplied

by a SCALING factor and the result is added to

the contents of a BASE register and a DISPLACE-

MENT to form the operand’s offset

13