M50LPW012 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

メーカー

M50LPW012 Datasheet PDF : 35 Pages

| |||

M50LPW012

Quadruple Byte Program Command. The Qua-

druple Byte Program Command can be only used

in A/A Mux mode to program four adjacent Bytes

in the memory array at a time. The four Bytes must

differ only for the addresses A0 and A1.

Programming should not be attempted when VPP

is not at VPPH. The operation can also be executed

if VPP is below VPPH, but result could be uncertain.

Five Bus Write operations are required to issue the

command. The second, the third and the fourth

Bus Write cycle latches respectively the address

and data of the first, the second and the third Byte

in the internal state machine. The fifth Bus Write

cycle latches the address and data of the fourth

Byte in the internal state machine and starts the

Program/Erase Controller. Once the command is

issued subsequent Bus Read operations read the

Status Register. See the section on the Status

Register for details on the definitions of the Status

Register bits.

During the Quadruple Byte Program operation the

memory will only accept the Read Status register

command and the Program/Erase Suspend com-

mand. All other commands will be ignored. Typical

Quadruple Byte Program times are given in Table

13.

Note that the Quadruple Byte Program command

cannot change a bit set to ‘0’ back to ‘1’ and

attempting to do so will not cause any modification

on its value. One of the Erase commands must be

used to set all of the bits in the block to ‘1’.

See Figure 14, Quadruple Byte Program Flow-

chart and Pseudo Code, for a suggested flowchart

on using the Quadruple Byte Program command.

Chip Erase Command. The Chip Erase Com-

mand can be only used in A/A Mux mode to erase

the entire chip at a time. Erasing should not be at-

tempted when VPP is not at VPPH. The operation

can also be executed if VPP is below VPPH, but re-

sult could be uncertain. Two Bus Write operations

are required to issue the command and start the

Program/Erase Controller. Once the command is

issued subsequent Bus Read operations read the

Status Register. See the section on the Status

Register for details on the definitions of the Status

Register bits. During the Chip Erase operation the

memory will only accept the Read Status Register

command. All other commands will be ignored.

Typical Chip Erase times are given in Table 13.

The Chip Erase command sets all of the bits in the

memory to ‘1’. See Figure 16, Chip Erase Flow-

chart and Pseudo Code, for a suggested flowchart

on using the Chip Erase command.

Block Erase Command. The Block Erase com-

mand can be used to erase a block. Two Bus Write

operations are required to issue the command; the

second Bus Write cycle latches the block address

in the internal state machine and starts the Pro-

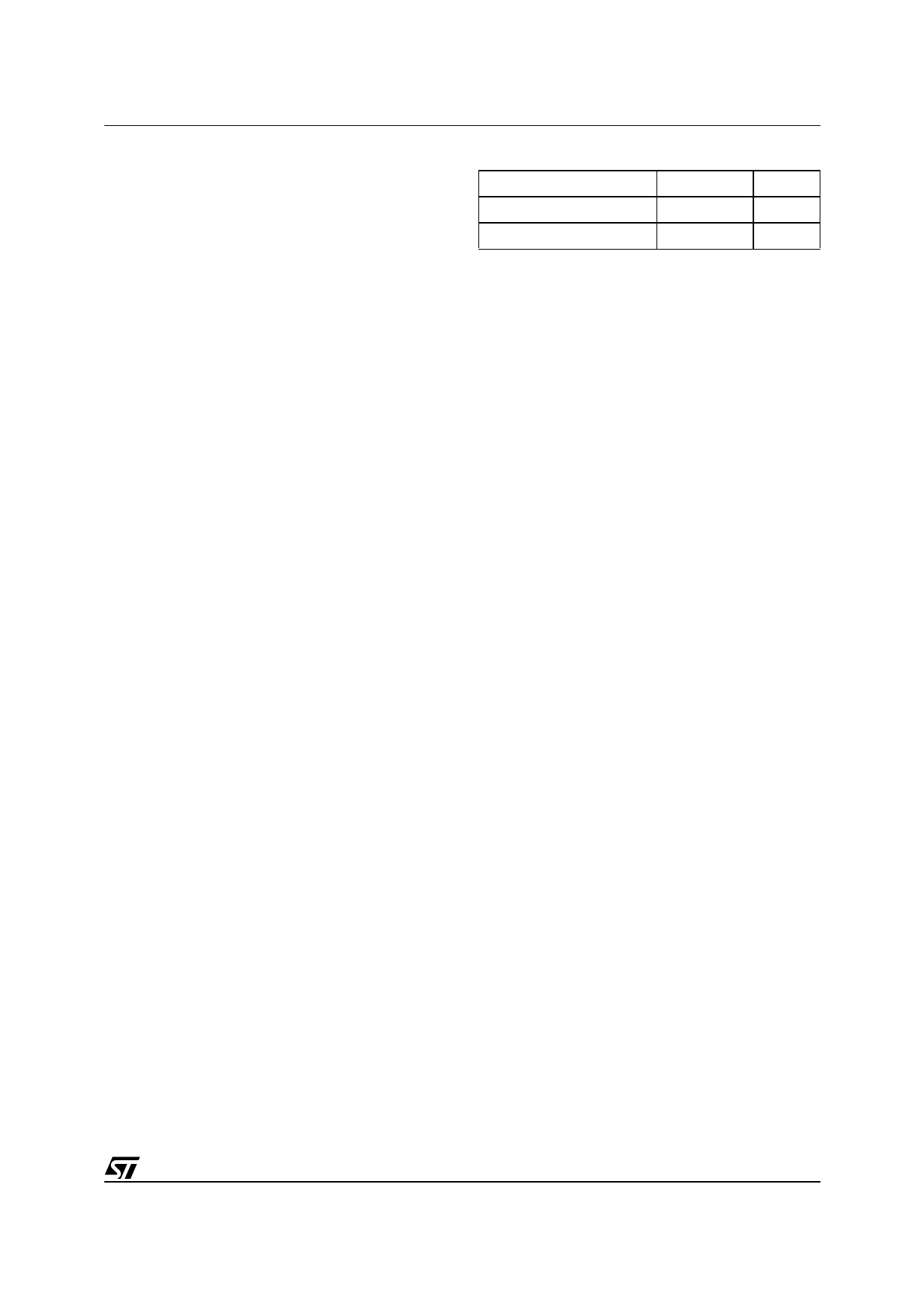

Table 11. Read Electronic Signature

Code

Address

Manufacturer Code

00000h

Device Code

00001h

Note: For A19:18 values, see Table 2.

Data

20h

3Bh

gram/Erase Controller. Once the command is is-

sued subsequent Bus Read operations read the

Status Register. See the section on the Status

Register for details on the definitions of the Status

Register bits.

If the block is protected then the Block Erase

operation will abort, the data in the block will not be

changed and the Status Register will output the

error.

During the Block Erase operation the memory will

only accept the Read Status Register command

and the Program/Erase Suspend command. All

other commands will be ignored. Typical Block

Erase times are given in Table 13.

The Block Erase command sets all of the bits in

the block to ‘1’. All previous data in the block is

lost.

See Figure 17, Block Erase Flowchart and Pseudo

Code, for a suggested flowchart on using the

Block Erase command.

Clear Status Register Command. The Clear Sta-

tus Register command can be used to reset bits 1,

3, 4 and 5 in the Status Register to ‘0’. One Bus

Write is required to issue the Clear Status Register

command. Once the command is issued the mem-

ory returns to its previous mode, subsequent Bus

Read operations continue to output the same data.

The bits in the Status Register are sticky and do

not automatically return to ‘0’ when a new Program

or Erase command is issued. If an error occurs

then it is essential to clear any error bits in the Sta-

tus Register by issuing the Clear Status Register

command before attempting a new Program or

Erase command.

Program/Erase Suspend Command. The Pro-

gram/Erase Suspend command can be used to

pause a Program or Block Erase operation. One

Bus Write cycle is required to issue the Program/

Erase Suspend command and pause the Pro-

gram/Erase Controller. Once the command is is-

sued it is necessary to poll the Program/Erase

Controller Status bit to find out when the Program/

Erase Controller has paused; no other commands

will be accepted until the Program/Erase Control-

ler has paused. After the Program/Erase Control-

ler has paused, the memory will continue to output

the Status Register until another command is is-

sued.

11/35