M80C286 データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

M80C286 Datasheet PDF : 60 Pages

| |||

M80C286

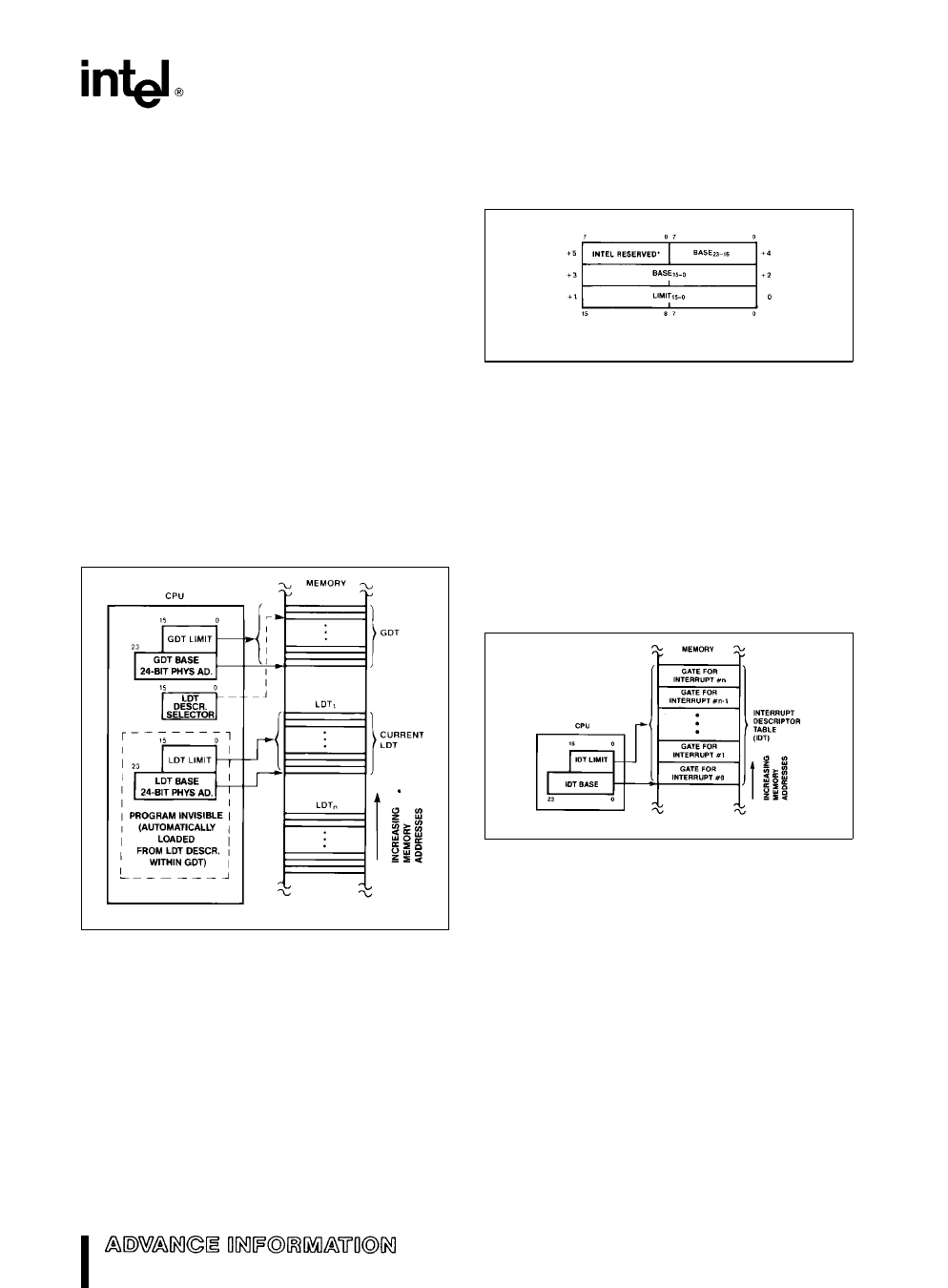

LOCAL AND GLOBAL DESCRIPTOR TABLES

Two tables of descriptors called descriptor tables

contain all descriptors accessible by a task at any

given time A descriptor table is a linear array of up

to 8192 descriptors The upper 13 bits of the selec-

tor value are an index into a descriptor table Each

table has a 24-bit base register to locate the descrip-

tor table in physical memory and a 16-bit limit regis-

ter that confine descriptor access to the defined lim-

its of the table as shown in Figure 16 A restartable

exception (13) will occur if an attempt is made to

reference a descriptor outside the table limits

One table called the Global Descriptor table (GDT)

contains descriptors available to all tasks The other

table called the Local Descriptor Table (LDT) con-

tains descriptors that can be private to a task Each

task may have its own private LDT The GDT may

contain all descriptor types except interrupt and trap

descriptors The LDT may contain only segment

task gate and call gate descriptors A segment can-

not be accessed by a task if its segment descriptor

does not exist in either descriptor table at the time of

access

The LDT instruction loads a selector which refers to

a Local Descriptor Table descriptor containing the

base address and limit for an LDT as shown in Fig-

ure 16

Must be set to 0 for compatibility with 80386

271103 – 15

Figure 17 Global Descriptor Table and

Interrupt Descriptor Table Data Type

INTERRUPT DESCRIPTOR TABLE

The protected mode M80C286 has a third descriptor

table called the Interrupt Descriptor Table (IDT)

(see Figure 18) used to define up to 256 interrupts

It may contain only task gates interrupt gates and

trap gates The IDT (Interrupt Descriptor Table) has

a 24-bit physical base and 16-bit limit register in the

CPU The privileged LIDT instruction loads these

registers with a six byte value of identical form to

that of the LGDT instruction (see Figure 17 and Pro-

tected Mode Initialization)

271103 – 14

Figure 16 Local and Global

Descriptor Table Definition

The LGDT and LLDT instructions load the base and

limit of the global and local descriptor tables LGDT

and LLDT are privileged i e they may only be exe-

cuted by trusted programs operating at level 0 The

LGDT instruction loads a six byte field containing the

16-bit table limit and 24-bit physical base address of

the Global Descriptor Table as shown in Figure 17

271103 – 16

Figure 18 Interrupt Descriptor Table Definition

References to IDT entries are made via INT instruc-

tions external interrupt vectors or exceptions The

IDT must be at least 256 bytes in size to allocate

space for all reserved interrupts

Privilege

The M80C286 has a four-level hierarchical privilege

system which controls the use of privileged instruc-

tions and access to descriptors (and their associat-

ed segments) within a task Four-level privilege as

shown in Figure 19 is an extension of the user su-

pervisor mode commonly found in minicomputers

The privilege levels are numbered 0 through 3

15