M80C286 データシートの表示(PDF) - Intel

部品番号

コンポーネント説明

メーカー

M80C286 Datasheet PDF : 60 Pages

| |||

M80C286

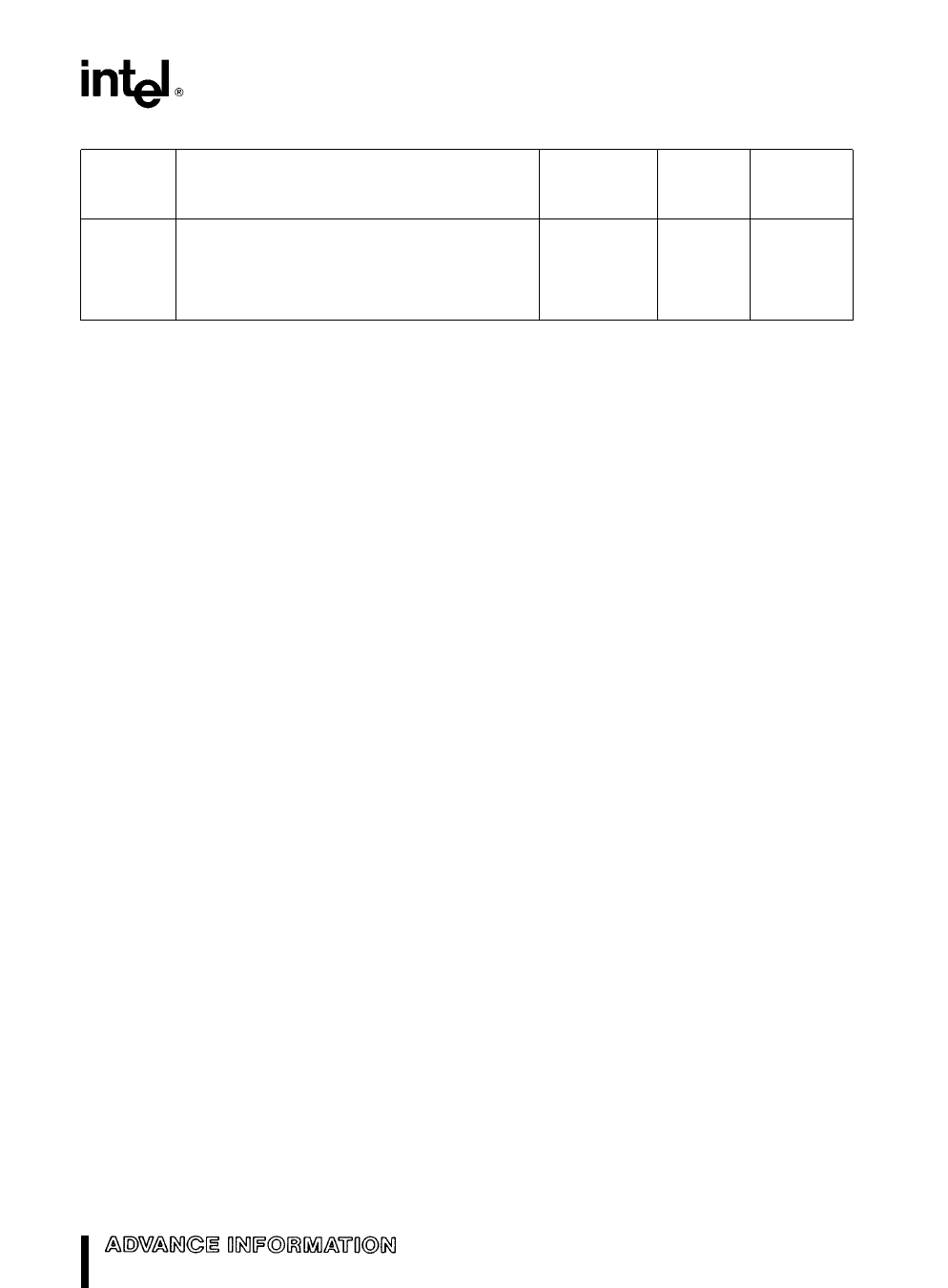

Table 14 Protected Mode Exceptions

Interrupt

Vector

8

9

10

11

12

13

Function

Double exception detected

Processor extension segment overrun

Invalid task state segment

Segment not present

Stack segment overrun or stack segment not present

General protection

Return

Address

At Falling

Instruction

Yes

No

Yes

Yes

Yes

Yes

Always

Restart-

able

No2

No2

Yes

Yes

Yes1

No2

Error

Code

on Stack

Yes

No

Yes

Yes

Yes

Yes

NOTE

1 When a PUSHA or POPA instruction attempts to wrap around the stack segment the machine state after the exception

will not be restartable because stack segment wrap around is not permitted This condition is identified by the value of the

saved SP being either 0000(H) 0001(H) FFFE(H) or FFFF(H)

2 These exceptions indicate a violation to privilege rules or usage rules has occurred Restart is generally not attempted

under those conditions

These exceptions indicate a violation to privilege

rules or usage rules has occurred Restart is gener-

ally not attempted under those conditions

All these checks are performed for all instructions

and can be split into three categories segment load

checks (Table 11) operand reference checks (Table

12) and privileged instruction checks (Table 13)

Any violation of the rules shown will result in an ex-

ception A not-present exception causes exception

11 or 12 and is restartable

Special Operations

TASK SWITCH OPERATION

The M80C286 provides a built-in task switch opera-

tion which saves the entire M80C286 execution

state (registers address space and a link to the pre-

vious task) loads a new execution state and com-

mences execution in the new task Like gates the

task switch operation is invoked by executing an in-

ter-segment JMP or CALL instruction which refers to

a Task State Segment (TSS) or task gate descriptor

in the GDT or LDT An INT n instruction exception

or external interrupt may also invoke the task switch

operation by selecting a task gate descriptor in the

associated IDT descriptor entry

The TSS descriptor points at a segment (see Figure

20) containing the entire M80C286 execution state

while a task gate descriptor contains a TSS selector

The limit field of the descriptor must be l002B(H)

Each task must have a TSS associated with it The

current TSS is identified by a special register in the

M80C286 called the Task Register (TR) This regis-

ter contains a selector referring to the task state

segment descriptor that defines the current TSS A

hidden base and limit register associated with TR

are loaded whenever TR is loaded with a new selec-

tor

The IRET instruction is used to return control to the

task that called the current task or was interrupted

Bit 14 in the flag register is called the Nested Task

(NT) bit It controls the function of the IRET instruc-

tion If NT e 0 the IRET instruction performs the

regular current task by popping values off the stack

when NT e 1 IRET performs a task switch opera-

tion back to the previous task

When a CALL JMP or INT instruction initiates a

task switch the old (except for case of JMP) and

new TSS will be marked busy and the back link field

of the new TSS set to the old TSS selector The NT

bit of the new task is set by CALL or INT initiated

task switches An interrupt that does not cause a

task switch will clear NT NT may also be set or

cleared by POPF or IRET instructions

The task state segment is marked busy by changing

the descriptor type field from Type 1 to Type 3 Use

of a selector that references a busy task state seg-

ment causes Exception 13

PROCESSOR EXTENSION CONTEXT

SWITCHING

The context of a processor extension (such as the

M80C287 numerics processor) is not changed by

the task switch operation A processor extension

context need only be changed when a different task

attempts to use the processor extension (which still

contains the context of a previous task) The

M80C286 detects the first use of a processor exten-

sion after a task switch by causing the processor

extension not present exception (7) The interrupt

handler may then decide whether a context change

is necessary

Whenever the M80C286 switches tasks it sets the

Task Switched (TS) bit of the MSW TS indicates

that a processor extension context may belong to a

different task than the current one The processor

extension not present exception (7) will occur when

attempting to execute an ESC or WAIT instruction if

TSe1 and a processor extension is present (MPe1

in MSW)

19