ISPLSI5384VE-80LF256 データシートの表示(PDF) - Lattice Semiconductor

部品番号

コンポーネント説明

メーカー

ISPLSI5384VE-80LF256 Datasheet PDF : 22 Pages

| |||

Specifications ispLSI 5384VE

Switching Test Conditions

Input Pulse Levels

Input Rise and Fall Time

GND to VCCIOmin

≤ 1.5ns 10% to 90%

Input Timing Reference Levels

1.5V

Ouput Timing Reference Levels

1.5V

Output Load

3-state levels are measured 0.5V from

steady-state active level.

See Figure 9

Table 2-0003/5KVE

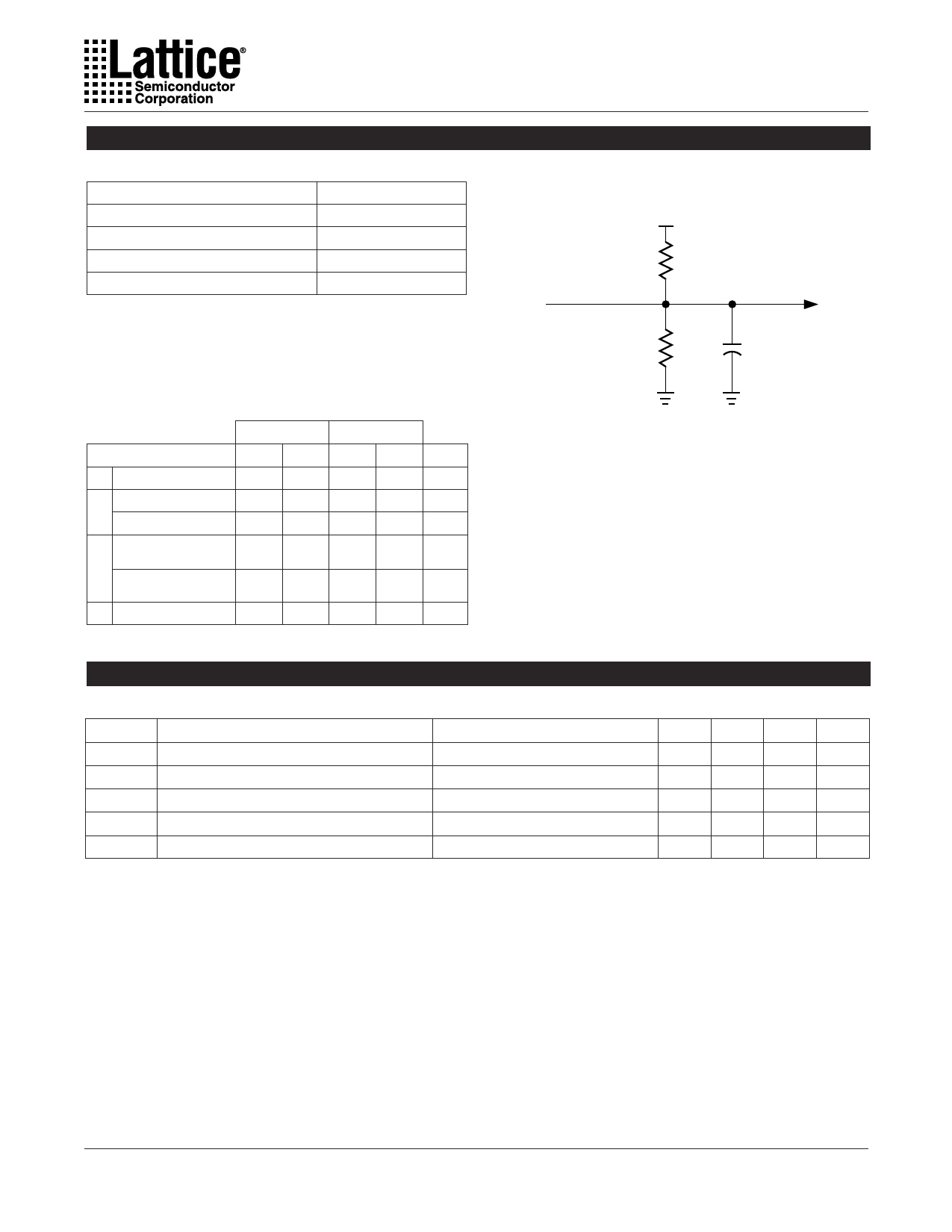

Figure 9. Test Load

Device

Output

VCCIO

R1

R2

Output Load Conditions (See Figure 9)

Test

Point

CL*

TEST CONDITION

A

Active High

B

Active Low

Active High to Z

C at VOH-0.5V

Active Low to Z

at VOL+0.5V

D Slow Slew

3.3V

2.5V

R1 R2 R1 R2 CL

316Ω 348Ω 511Ω 475Ω 35pF

∞ 348Ω ∞ 475Ω 35pF

316Ω ∞ 511Ω ∞ 35pF

∞ 348Ω ∞ 475Ω 5pF

*CL includes Test Fixture and Probe Capacitance.

0213D

316Ω ∞ 511Ω ∞ 5pF

∞

∞

∞

∞ 35pF

Table 2-0004A/5KVE

DC Electrical Characteristics for 3.3V Range1

Over Recommended Operating Conditions

SYMBOL

PARAMETER

VCCIO I/O Reference Voltage

VIL

Input Low Voltage

VIH

Input High Voltage

VOL

Output Low Voltage

VOH

Output High Voltage

1. I/O voltage configuration must be set to VCC.

CONDITION

VCCIO = min, IOL = 8 mA

VCCIO = min, IOH = -4 mA

MIN.

3.0

-0.3

2.0

–

2.4

TYP.

–

–

–

–

–

MAX. UNITS

3.6

V

0.8

V

5.25 V

0.4

V

–

V

Table 2-0007/5KVE

11