IDT79R3500 データシートの表示(PDF) - Integrated Device Technology

部品番号

コンポーネント説明

メーカー

IDT79R3500 Datasheet PDF : 16 Pages

| |||

IDT79R3500 RISC CPU PROCESSOR RISCore

MILITARY AND COMMERCIAL TEMPERATURE RANGES

dispatches). Branches have 16-bit offsets relative to the

program counter (I-type). Jump and Link instructions save

a return address in Register 31. The R3500 instruction set

features a number of branch conditions. Included is the

ability to compare a register to zero and branch, and also

the ability to branch based on a comparison between two

registers. Thus, net performance is increased since soft-

ware does not have to perform arithmetic instructions prior

to the branch to set up the branch conditions.

• Coprocessor instructions perform operations in the

coprocessors. Coprocessor Loads and Stores are I-type.

• Coprocessor 0instructions perform operations on the Sys-

tem Control Coprocessor (CP0) registers to manipulate

the memory management and exception handling facilities

of the processor.

• Special instructions perform a variety of tasks, including

movement of data between special and general registers,

system calls, and breakpoint. They are always R-type.

SYSTEM CONTROL COPROCESSOR (CP0)

INSTRUCTIONS

Register

Description

EntryHi

EntryLo

Index

Random

High half of a TLB entry

Low half of a TLB entry

Programmable pointer into TLB array

Pseudo-random pointer into TLB array

Status

Cause

EPC

Context

BadVA

Mode, interrupt enables, and diagnostic status info

Indicates nature of last exception

Exception Program Counter

Pointer into kernel’s virtual Page Table Entry array

Most recent bad virtual address

PRId Processor revision identification (Read only)

2871 tbl 02

Table 1 lists the instruction set of the IDT79R3500 processor.

STATUS

CAUSE

EPC

IDT79R3500 System Control Coprocessor (CP0)

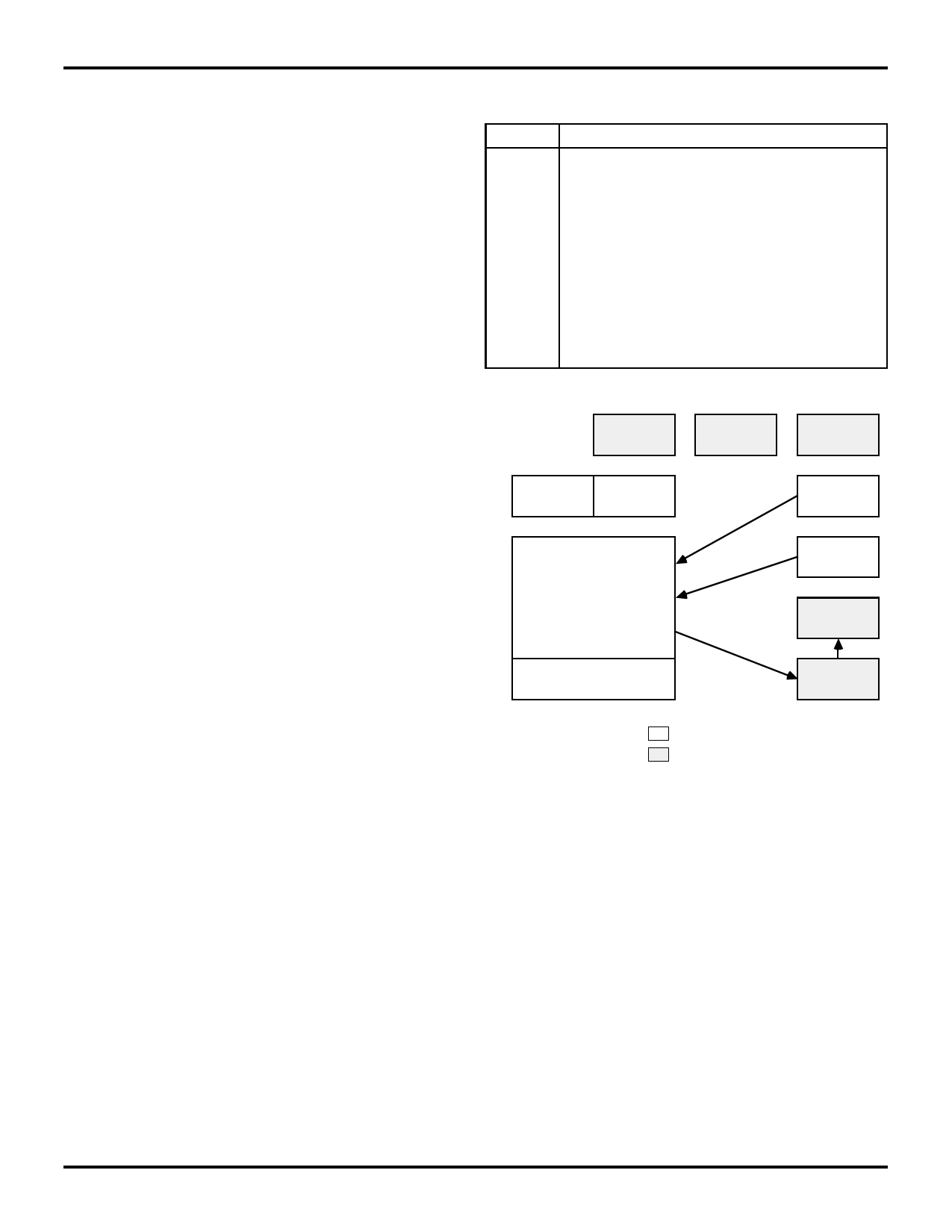

The IDT79R3500 can operate with up to four tightly-

coupled coprocessors (designated CP0 through CP3). The

System Control Coprocessor (or CP0), is incorporated on the

IDT79R3500 chip and supports the virtual memory system

and exception handling functions of the IDT79R3500. The

virtual memory system is implemented using a Translation

Lookaside Buffer and a group of programmable registers as

shown in Figure 5.

System Control Coprocessor (CP0) Registers

The CP0 registers shown in Figure 5 are used to control

the memory management and exception handling capabilities

of the IDT79R3500. Table 2 provides a brief description of

each register.

ENTRYHI ENTRYLO

INDEX

63

RANDOM

TLB

CONTEXT

8

7

NOT ACCESSED

BY RANDOM

0

BADVA

Used with Virtual Memory System

Used with Exception Processing

2871 drw 05

Figure 5. The System Coprocessor Registers